|

|

PDF AT25DF641A Data sheet ( Hoja de datos )

| Número de pieza | AT25DF641A | |

| Descripción | 64-Mbit 2.7V Minimum Serial Peripheral Interface Serial Flash Memory | |

| Fabricantes | ATMEL Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AT25DF641A (archivo pdf) en la parte inferior de esta página. Total 57 Páginas | ||

|

No Preview Available !

Features

• Single 2.7V - 3.6V Supply

• Serial Peripheral Interface (SPI) Compatible

– Supports SPI Modes 0 and 3

– Supports Atmel RapidS Operation

– Supports Dual-Input Program and Dual-Output Read

• Very High Operating Frequencies

– 100MHz for RapidS

– 85MHz for SPI

– Clock-to-Output (tV) of 5ns Maximum

• Flexible, Optimized Erase Architecture for Code + Data Storage Applications

– Uniform 4-Kbyte Block Erase

– Uniform 32-Kbyte Block Erase

– Uniform 64-Kbyte Block Erase

– Full Chip Erase

• Individual Sector Protection with Global Protect/Unprotect Feature

– 128 Sectors of 64-Kbytes Each

• Hardware Controlled Locking of Protected Sectors via WP Pin

• Sector Lockdown

– Make Any Combination of 64-Kbyte Sectors Permanently Read-Only

• 128-Byte Programmable OTP Security Register

• Flexible Programming

– Byte/Page Program (1- to 256-Bytes)

• Fast Program and Erase Times

– 1.0ms Typical Page Program (256-Bytes) Time

– 50ms Typical 4-Kbyte Block Erase Time

– 250ms Typical 32-Kbyte Block Erase Time

– 400ms Typical 64-Kbyte Block Erase Time

• Program and Erase Suspend/Resume

• Automatic Checking and Reporting of Erase/Program Failures

• Software Controlled Reset

• JEDEC Standard Manufacturer and Device ID Read Methodology

• Low Power Dissipation

– 5mA Active Read Current (Typical at 20MHz)

– 5µA Deep Power-Down Current (Typical)

• Endurance: 100,000 Program/Erase Cycles

• Data Retention: 20 Years

• Complies with Full Industrial Temperature Range

• Industry Standard Green (Pb/Halide-free/RoHS Compliant) Package Options

– 8-lead SOIC (208-mil wide)

– 8-contact Ultra Thin DFN (5mm x 6mm x 0.6mm)

64-Mbit

2.7V Minimum

Serial Peripheral

Interface Serial

Flash Memory

Atmel AT25DF641A

Preliminary

8693A–DFLASH–8/10

1 page

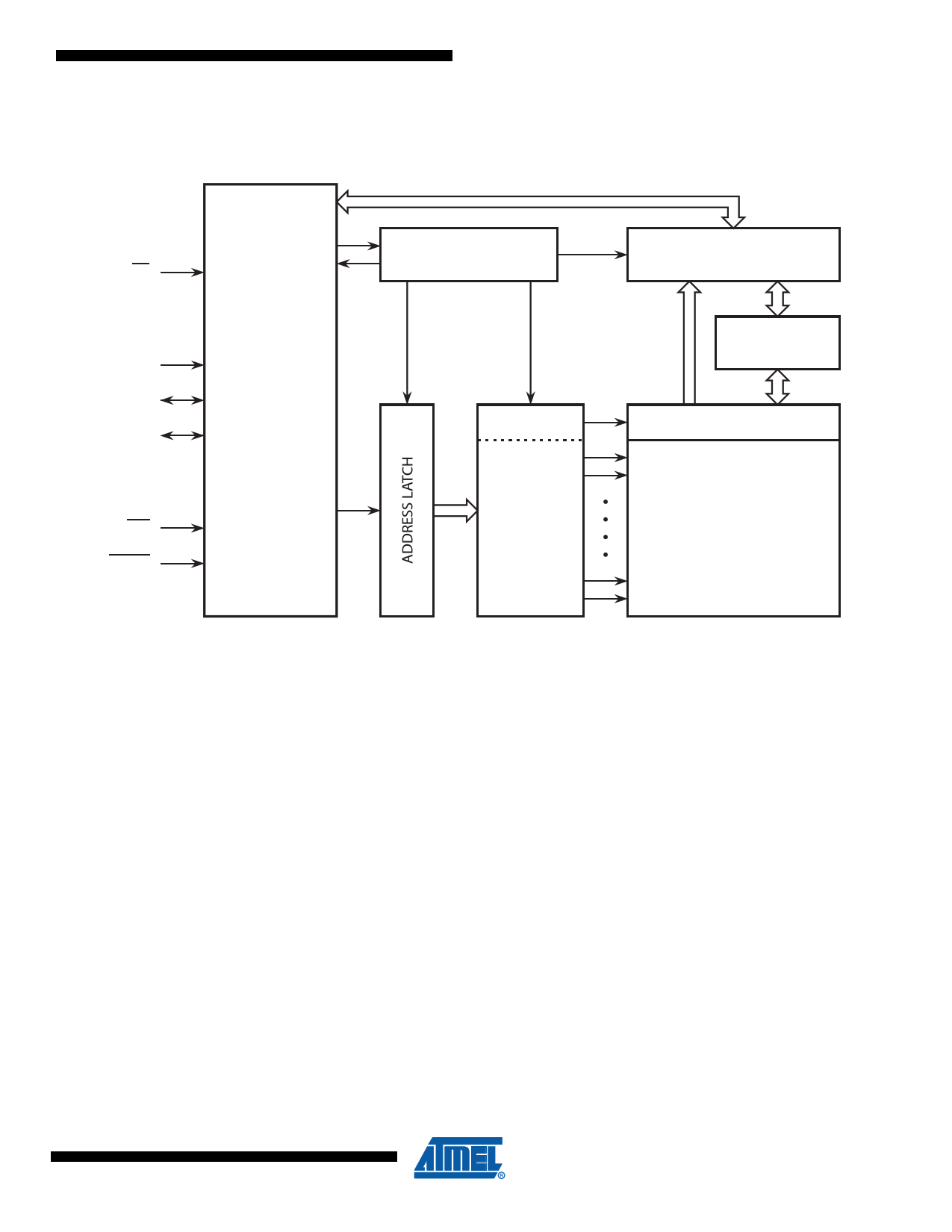

3. Block Diagram

Figure 3-1. Block Diagram

CS

SCK

SI (SIO)

SO (SOI)

WP

HOLD

INTERFACE

CONTROL

AND

LOGIC

Atmel AT25DF641A [Preliminary]

CONTROL AND

PROTECTION LOGIC

Y-DECODER

X-DECODER

I/O BUFFERS

AND LATCHES

SRAM

DATA BUFFER

Y-GATING

FLASH

MEMORY

ARRAY

4. Memory Array

To provide the greatest flexibility, the memory array of the Atmel® AT25DF641A can be erased

in four levels of granularity including a full chip erase. In addition, the array has been divided into

physical sectors of uniform size, of which each sector can be individually protected from pro-

gram and erase operations. The size of the physical sectors is optimized for both code and data

storage applications, allowing both code and data segments to reside in their own isolated

regions. The Memory Architecture Diagram illustrates the breakdown of each erase level as well

as the breakdown of each physical sector.

8693A–DFLASH–8/10

5

5 Page

Atmel AT25DF641A [Preliminary]

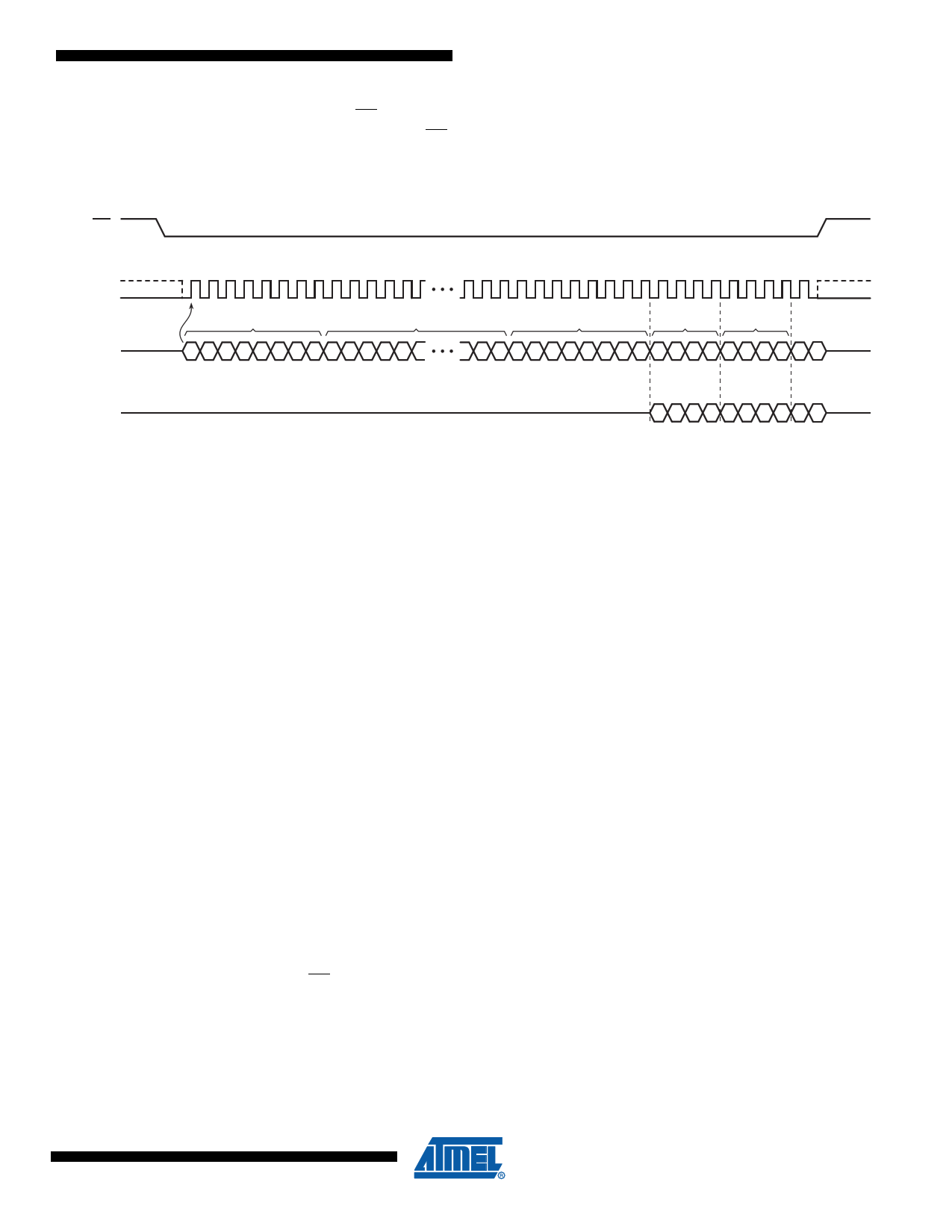

Deasserting the CS pin will terminate the read operation and put the SO and SIO pins into a

high-impedance state. The CS pin can be deasserted at any time and does not require that a full

byte of data be read.

Figure 7-4. Dual-Output Read Array

CS

SCK

SIO

SO

0 1 2 3 4 5 6 7 8 9 10 11 12

29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48

OPCODE

ADDRESS BITS A23-A0

DON'T CARE

OUTPUT

DATA BYTE 1

OUTPUT

DATA BYTE 2

00 111011AAAAAA

MSB MSB

A A A X X X X X X X X D6 D4 D2 D0 D6 D4 D2 D0 D6 D4

MSB

HIGH-IMPEDANCE

D7 D5 D3 D1 D7 D5 D3 D1 D7 D5

MSB MSB MSB

8. Program and Erase Commands

8.1 Byte/Page Program

The Byte/Page Program command allows anywhere from a single byte of data to 256-bytes of

data to be programmed into previously erased memory locations. An erased memory location is

one that has all eight bits set to the logical “1” state (a byte value of FFh). Before a Byte/Page

Program command can be started, the Write Enable command must have been previously

issued to the device (see “Write Enable” on page 20) to set the Write Enable Latch (WEL) bit of

the Status Register to a logical “1” state.

To perform a Byte/Page Program command, an opcode of 02h must be clocked into the device

followed by the three address bytes denoting the first byte location of the memory array to begin

programming at. After the address bytes have been clocked in, data can then be clocked into the

device and will be stored in an internal buffer.

If the starting memory address denoted by A23-A0 does not fall on an even 256-byte page

boundary (A7-A0 are not all 0), then special circumstances regarding which memory locations to

be programmed will apply. In this situation, any data that is sent to the device that goes beyond

the end of the page will wrap around back to the beginning of the same page. For example, if the

starting address denoted by A23-A0 is 0000FEh, and three bytes of data are sent to the device,

then the first two bytes of data will be programmed at addresses 0000FEh and 0000FFh while

the last byte of data will be programmed at address 000000h. The remaining bytes in the page

(addresses 000001h through 0000FDh) will not be programmed and will remain in the erased

state (FFh). In addition, if more than 256-bytes of data are sent to the device, then only the last

256 bytes sent will be latched into the internal buffer.

When the CS pin is deasserted, the device will take the data stored in the internal buffer and pro-

gram it into the appropriate memory array locations based on the starting address specified by

A23-A0 and the number of data bytes sent to the device. If less than 256-bytes of data were sent

to the device, then the remaining bytes within the page will not be programmed and will remain

in the erased state (FFh). The programming of the data bytes is internally self-timed and should

take place in a time of tPP or tBP if only programming a single byte.

8693A–DFLASH–8/10

11

11 Page | ||

| Páginas | Total 57 Páginas | |

| PDF Descargar | [ Datasheet AT25DF641A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AT25DF641 | 64-Megabit 2.7-volt Minimum SPI Serial Flash Memory | ATMEL Corporation |

| AT25DF641A | 2.7V Minimum SPI Serial Flash Memory | Adesto |

| AT25DF641A | 64-Mbit 2.7V Minimum Serial Peripheral Interface Serial Flash Memory | ATMEL Corporation |

| AT25DF641A-MH-T | 2.7V Minimum SPI Serial Flash Memory | Adesto |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |