|

|

PDF NB3F8L3005C Data sheet ( Hoja de datos )

| Número de pieza | NB3F8L3005C | |

| Descripción | 3.3V / 2.5V / 1.8V / 1.5V 2:1:5 LVCMOS Fanout Buffer | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NB3F8L3005C (archivo pdf) en la parte inferior de esta página. Total 13 Páginas | ||

|

No Preview Available !

NB3F8L3005C

3.3V / 2.5V / 1.8V / 1.5V

2:1:5 LVCMOS Fanout Buffer

Description

The NB3F8L3005C is a 2:1:5 Clock / Data fanout buffer operating

on a 3.3 V / 2.5 V Core VDD and two flexible 3.3 V / 2.5 V / 1.8 V /

1.5 V VDDOx supplies which must be equal or less than VDD.

A Mux selects between a Crystal input, or a differential/SE Clock /

Data inputs. Differential Inputs accept LVPECL, LVDS, HCSL, or

SSTL and Single−Ended levels. The MUX control line, SEL selects

CLK/CLK, or Crystal input pins per Table 3. The Crystal input is

disabled when a Clock input is selected. Output enable pin, OE,

synchronously forces a High Impedance state (Hi−Z) when Low per

Table 4.

Outputs consist of five single−ended LVCMOS outputs.

www.onsemi.com

QFN24

G SUFFIX

CASE 485DJ

MARKING

DIAGRAM

1

NB3F8L

3005C

ALYWG

G

Features

• Five LVCMOS / LVTTL Outputs up to 200 MHz

• Differential Inputs Accept LVPECL, LVDS, HCSL, SSTL, or

LVCMOS/LVTTL

• Crystal Interface

• Crystal Input Frequency Range: 10 MHz to 50 MHz

• Output Skew: 10 ps Typical

• Additive RMS Phase Jitter @ 156.25 MHz, (12 kHz – 20 MHz):

0.03 ps (Typical)

• Synchronous Output Enable

• Output Defined Level When Input is Floating

• Power Supply Modes:

♦ Single 3.3 V ± 5%

♦ Single 2.5 V ± 5%

♦ Mixed 3.3 V ± 5% Core/2.5 V ± 5% Output Operating Supply

♦ Mixed 3.3 V ± 5% Core/1.8 V ± 0.2 V Output Operating Supply

♦ Mixed 3.3 V ± 5% Core/1.5 V ± 0.15 V Output Operating Supply

♦ Mixed 2.5 V ± 5% Core/ 1.8 V ± 0.2 V Output Operating Supply

♦ Mixed 2.5 V ± 5% Core /1.5 V ± 0.15 V Output Operating Supply

• Two Separate Output Bank Power Supplies

• Industrial Temperature Range: −40°C to 85°C

• These are Pb−Free Devices

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

G = Pb−Free Package

(Note: Microdot may be in either location)

ORDERING INFORMATION

See detailed ordering and shipping information on page 12 of

this data sheet.

Applications

• Clock Distribution

• Networking and Communications

• High End Computing

• Wireless and Wired Infrastructure

End Products

• Servers

• Ethernet Switch/Routers

• ATE

• Test and Measurement

© Semiconductor Components Industries, LLC, 2015

April, 2015 − Rev. 1

1

Publication Order Number:

NB3F8L3005C/D

1 page

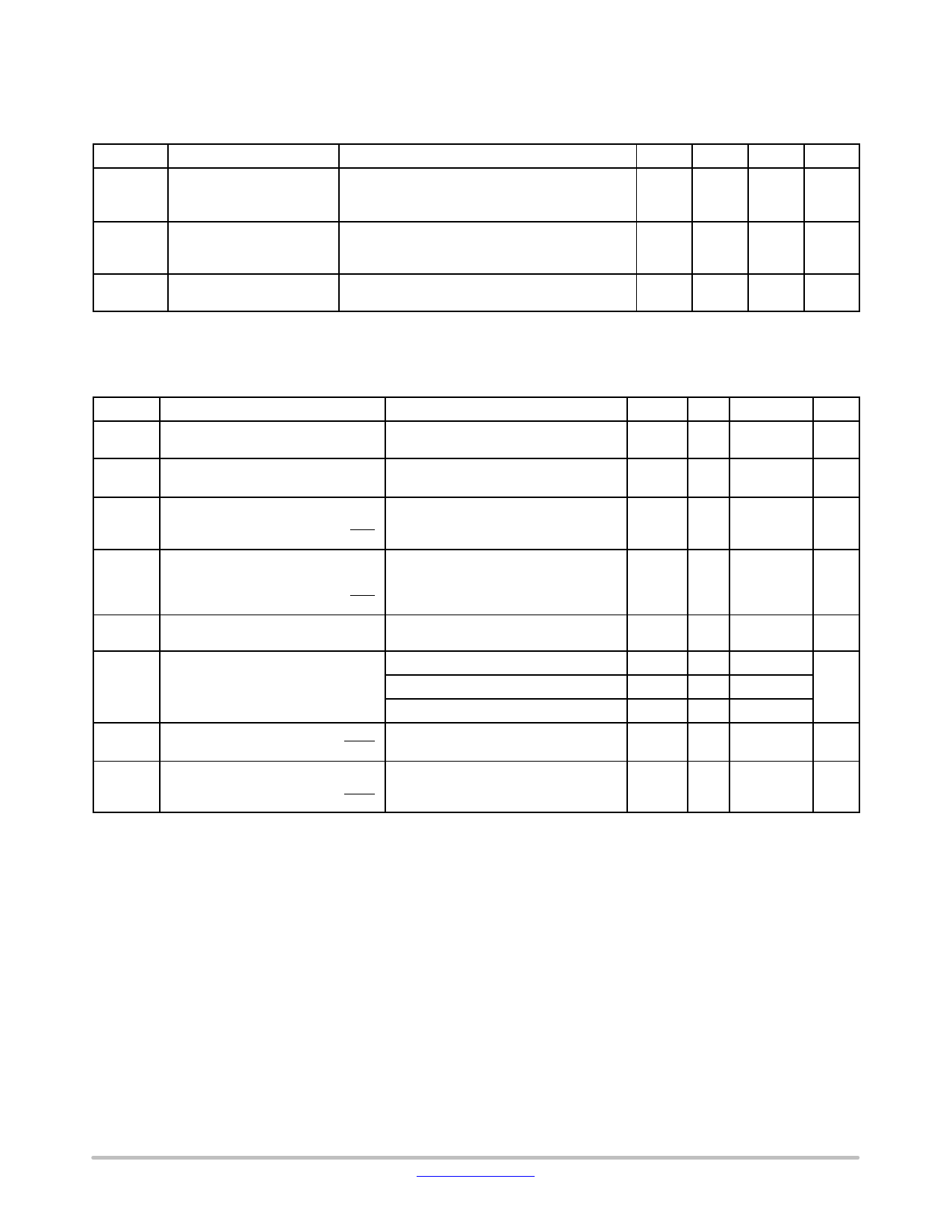

NB3F8L3005C

Table 9. POWER SUPPLY CHARACTERISTICS VDD ≥ VDDO; VDD = 3.3 V ± 5% (3.135 V to 3.465 V) or VDD = 2.5 V ±5%

(2.375 V to 2.625 V) and VDDOx = 3.3 V ± 5% (3.135 V to 3.465 V) or 2.5 V ± 5% (2.375 V to 2.625 V) or 1.8 V ± 0.2 V (1.6 V to 2.0 V)

or 1.5 V ± 0.15 V (1.35 V to 1.65 V); TA = −40°C to 85°C

Symbol

Parameter

Test Conditions

Min Typ Max Unit

IDD VDD Power Supply Current

fIN = 0 MHz

VDDO = 3.3 V, fIN = 100 MHz

VDDO = 2.5 V, fIN = 100 MHz

30 38 mA

30

20

IDDO

IDD +

IDDO

VDDO Power Supply

Current

Total Device Current with

Loads on All Outputs

OE = 0, no load

VDDO = 3.3 V, OE = 1, fIN = 100 MHz

VDDO = 2.5 V, OE = 1, fIN = 100 MHz

OE = 1, fIN = 100 MHz

OE = 0

0.1 mA

7

5

48 mA

16

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit

board with maintained transverse airflow greater than 500 lfpm.

Table 10. DC CHARACTERISTICS TA = −40°C to 85°C

Symbol

Parameter

Test Conditions

Min Typ Max Unit

VIH LVCMOS / LVTTL Input High Voltage

(OE, SEL)

VDD = 3.3 V ±5%

VDD = 2.5 V ± 5%

VIL LVCMOS / LVTTL Input Low Voltage

(OE, SEL)

VDD = 3.3 V ±5%

VDD = 2.5 V ± 5%

IIH Input High Current

OE, SEL

CLK/CLK

VDD = VIN = 3.465 V

VDD = VIN = 3.465 V or 2.625 V

IIL Input Low Current

OE, SEL

CLK

CLK

VDD = 3.465 V; VIN = 0.0 V

VDD = 3.465 V or 2.625 V VIN = 0.0 V

VDD = 3.465 V or 2.625 V VIN = 0.0 V

VOH Output High Voltage

VOL

VPP

VIHCMR

Output Low Voltage

Peak−to−Peak Input Voltage

VIL > −0.3 V

CLKx/CLKx

Input High Level Common Mode

Range

VCM = VIH; VIL > −0.3 V CLKx/CLKx

VDDOx = 3.3 V ± 5% or 2.5 V ± 5%

VDDOx = 1.8 V ± 0.2 V

VDDOx = 1.5 V ± 0.15 V

VDD = 3.3 V ±5% or VDD = 2.5 V ± 5%

VDD = 3.3 V ±5% or VDD = 2.5 V ± 5%

1.6

1.3

−0.3

−0.3

−5

−5

−150

VDDO

− 0.1

0.15

0.5

VDD + 0.3

VDD + 0.3

0.8

0.4

100

100

5

V

V

mA

mA

V

0.5 V

0.4

0.37

1.3 V

VDD − 0.85

V

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit

board with maintained transverse airflow greater than 500 lfpm.

www.onsemi.com

5

5 Page

NB3F8L3005C

Differential Clock Input Interface

The CLK / CLK accept LVDS, LVPECL, SSTL, HCSL

differential signals. Signals must meet the VPP and VCMR

input requirements. Figures 9 to 13 show interface

examples for the CLK / CLK input with built−in 50 W

terminations driven by the most common driver types. The

input interfaces suggested here are examples only. If the

driver is from another vendor, use their termination

recommendation. Please consult with the vendor of the

driver component to confirm the driver termination

requirements.

VDD = +3.3 V

Qx

LVPECL

Qx

GND = 0.0 V

VDD = +3.3 V

VDD = +3.3 V

125 W

Zo = 50 W

Zo = 50 W

125 W

CLKx

Differential

CLKx

In

84 W

84 W

GND = 0.0 V

GND = 0.0 V

Figure 9. CLK / CLK Input Driven by 3.3 V LVPECL

Driver (Thevenin Parallel Termination)

VDD = +3.3 V

VDD = +3.3 V

Qx

LVPECL

Qx

Zo = 50 W

Zo = 50 W

50 W

CLKx

Differential

CLKx

In

50 W

GND = 0.0 V

50 W

GND = 0.0 V

GND = 0.0 V

Figure 10. CLK / CLK Input Driven by 3.3 V

LVPECL Driver (“Y” Parallel Termination)

VDD = +3.3 V

VDD = +3.3 V

Qx 33 W (Opt)

HCSL

Qx 33 W (Opt)

50 W

GND = 0.0 V

Zo = 50 W

Zo = 50 W

CLKx

Differential

CLKx

In

50 W

GND = 0.0 V

GND = 0.0 V

VDD = +3.3 V

Qx

LVDS

Qx

GND = 0.0 V

Zo = 50 W

Zo = 50 W

100 W

VDD = +3.3 V

CLKx

Differential

CLKx

In

GND = 0.0 V

Figure 11. CLK / CLK Input Driven by a 3.3 V

HCSL Driver

Figure 12. CLK / CLK Input Driven by 3.3 V

LVDS Driver

VDD = +2.5 V

Qx

SSTL

Qx

VDD = +2.5 V

VDD = +3.3 V

120 W

Zo = 50 W

Zo = 50 W

120 W

CLKx

Differential

CLKx

In

120 W

120 W

GND = 0.0 V

GND = 0.0 V

GND = 0.0 V

Figure 13. CLK / CLK Input Driven by 2.5 V SSTL Driver

www.onsemi.com

11

11 Page | ||

| Páginas | Total 13 Páginas | |

| PDF Descargar | [ Datasheet NB3F8L3005C.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NB3F8L3005C | 3.3V / 2.5V / 1.8V / 1.5V 2:1:5 LVCMOS Fanout Buffer | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |