|

|

PDF STR755FR0 Data sheet ( Hoja de datos )

| Número de pieza | STR755FR0 | |

| Descripción | 32-bit MCU | |

| Fabricantes | STMicroelectronics | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de STR755FR0 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

STR750Fxx STR751Fxx

STR752Fxx STR755Fxx

ARM7TDMI-S™ 32-bit MCU with Flash, SMI, 3 std 16-bit timers,

PWM timer, fast 10-bit ADC, I2C, UART, SSP, USB and CAN

Features

■ Core

– ARM7TDMI-S 32-bit RISC CPU

– 54 DMIPS @ 60 MHz

■ Memories

– Up to 256 KB Flash program memory (10k

W/E cycles, retention 20 yrs @ 85°C)

– 16 KB Read-While-Write Flash for data

(100k W/E cycles, retention 20 yrs@ 85°C)

– Flash Data Readout and Write Protection

– 16KBytes embedded high speed SRAM

– Memory mapped interface (SMI) to ext.

Serial Flash (64 MB) w. boot capability

■ Clock, reset and supply management

– Single supply 3.3V ±10% or 5V ±10%

– Embedded 1.8V Voltage Regulators

– Int. RC for fast start-up and backup clock

– Up to 60 MHz operation using internal PLL

with 4 or 8 MHz crystal/ceramic osc.

– Smart Low Power Modes: SLOW, WFI,

STOP and STANDBY with backup registers

– Real-time Clock, driven by low power

internal RC or 32.768 kHz dedicated osc,

for clock-calendar and Auto Wake-up

■ Nested interrupt controller

– Fast interrupt handling with 32 vectors

– 16 IRQ priorities, 2 maskable FIQ sources

– 16 external interrupt / wake-up lines

■ DMA

– 4-channel DMA controller

– Circular buffer management

– Support for UART, SSP, Timers, ADC

■ 6 Timers

– 16-bit watchdog timer (WDG)

– 16-bit timer for system timebase functions

– 3 synchronizable timers each with up to 2

input captures and 2 output

compare/PWMs.

LQFP64 10x10 mm LQFP100 14 x 14 mm

LFBGA64

8 x 8 x 1.7 mm

LFBGA100

10 x 10 x 1.7 mm

– 16-bit 6-ch. synchronizable PWM timer

– Dead time generation, edge/center-aligned

waveforms and emergency stop

– Ideal for induction/brushless DC motors

■ 8 Communications interfaces

– 1 I2C interface

– 3 HiSpeed UARTs w. Modem/LIN capability

– 2 SSP interfaces (SPI or SSI) up to 16 Mb/s

– 1 CAN interface (2.0B Active)

– 1 USB full-speed 12 Mb/s interface with 8

configurable endpoint sizes

■ 10-bit A/D converter

– 16/11 chan. with prog. Scan Mode & FIFO

– Programmable Analog Watchdog feature

– Conversion time: min. 3.75 µs

– Start conversion can be triggered by timers

■ Up to 72/38 I/O ports

– 72/38 GPIOs with High Sink capabilities

– Atomic bit SET and RES operations

Table 1. Device summary

Reference

Part number

STR750Fxx STR750FV0, STR750FV1, STR750FV2

STR751Fxx STR751FR0, STR751FR1, STR751FR2

STR752Fxx STR752FR0, STR752FR1, STR752FR2

STR755Fxx

STR755FR0, STR755FR1, STR755FR2

STR755FV0, STR755FV1, STR755FV2

February 2009

Rev 5

1/84

www.st.com

1

1 page

STR750Fxx STR751Fxx STR752Fxx STR755Fxx

3 Introduction

Introduction

This Datasheet contains the description of the STR750F family features, pinout, Electrical

Characteristics, Mechanical Data and Ordering information.

For complete information on the Microcontroller memory, registers and peripherals. Please

refer to the STR750F Reference Manual.

For information on the ARM7TDMI-S core please refer to the ARM7TDMI-S Technical

Reference Manual available from Arm Ltd.

For information on programming, erasing and protection of the internal Flash memory

please refer to the STR7 Flash Programming Reference Manual

For information on third-party development tools, please refer to the http://www.st.com/mcu

website.

3.1 Functional description

The STR750F family includes devices in 2 package sizes: 64-pin and 100-pin. Both types

have the following common features:

ARM7TDMI-STM core with embedded Flash & RAM

STR750F family has an embedded ARM core and is therefore compatible with all ARM tools

and software. It combines the high performance ARM7TDMI-STM CPU with an extensive

range of peripheral functions and enhanced I/O capabilities. All devices have on-chip high-

speed single voltage FLASH memory and high-speed RAM.

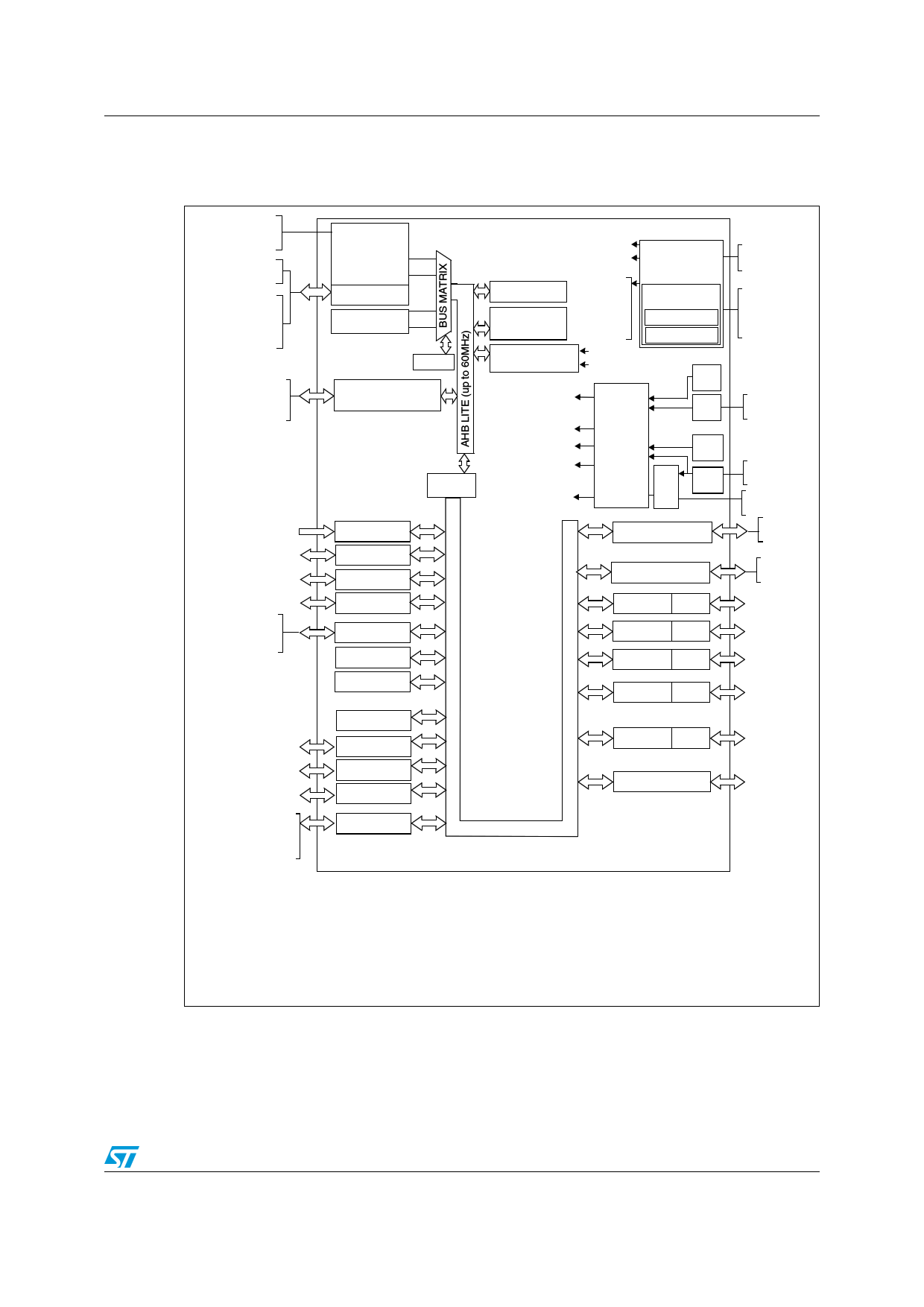

Figure 1 shows the general block diagram of the device family.

Embedded Flash memory

Up to 256 KBytes of embedded Flash is available in Bank 0 for storing programs and data.

An additional Bank 1 provides 16 Kbytes of RWW (Read While Write) memory allowing it to

be erased/programmed on-the-fly. This partitioning feature is ideal for storing application

parameters.

● When configured in burst mode, access to Flash memory is performed at CPU clock

speed with 0 wait states for sequential accesses and 1 wait state for random access

(maximum 60 MHz).

● When not configured in burst mode, access to Flash memory is performed at CPU

clock speed with 0 wait states (maximum 32 MHz)

Embedded SRAM

16 Kbytes of embedded SRAM accessed (read/write) at CPU clock speed with 0 wait states.

Enhanced interrupt controller (EIC)

In addition to the standard ARM interrupt controller, the STR750F embeds a nested interrupt

controller able to handle up to 32 vectors and 16 priority levels. This additional hardware

block provides flexible interrupt management features with minimal interrupt latency.

5/84

5 Page

STR750Fxx STR751Fxx STR752Fxx STR755Fxx

Introduction

3.2

Block diagram

Figure 1. STR750 block diagram

BOOT1,

BOOT0

as AF

TEST

NJTRST

JTDI

JTCK

JTMS

JTDO

as AF

SCLK, MOSI

MISO as AF

4 CS as AF

15AF

P0[31:0]

P1[19:0]

P2[19:0]

16AF

VDDA_ADC

VSSA_ADC

2xICAP, 2xOCMP

as AF

2xICAP, 2xOCMP

as AF

2xICAP, 2xOCMP

as AF

PWM1, PWM1N

PWM2, PWM2N

PWM3, PWM3N

PWM_EMERGENCY

as AF

ARM7TDMI-S

CPU

60MHz AHB

JTAG & ICE-RT

GP DMA

4 streams

AHB

Arbiter

SERIAL MEMORY

INTERFACE

APB

BRIDGE

EXT.IT

WAKEUP

GPIO PORT 0

GPIO PORT 1

GPIO PORT 2

10-bit ADC

WATCHDOG

RTC

TB TIMER

TIM0 TIMER

TIM1 TIMER

TIM2 TIMER

HRESETN

PRESETN

RESET &

POWER

SRAM 16KB

FLASH 256KB

+16KB (RWW)

VDD_IO

VCORE

VBACKUP

VDDA_PLL

VDDA_ADC

DC-DC

3.3V TO 1.8V

MAIN

LOW POWER

NESTED

32xIRQ

INTERRUPT CTL 2xFIQ

LP

OSC

CK_RTC

OSC

32K

CK_SYS

HCLK

PCLK

CK_USB

CLOCK

MANAGE-

MENT

PLL

FREE

OSC

OSC

4M

USB Full Speed

CAN 2.0B

FIFO

2x(16x8bit)

UART0

FIFO

2x(16x8bit)

UART1

FIFO

2x(16x8bit)

UART2

FIFO

2x(8x16bit)

SSP0

FIFO

2x(8x16bit)

SSP1

I2C

NRSTIN

NRSTOUT

VDD_IO

V18

V18BKP

VSS

RTC_XT1

RTC_XT2

XT1

XT2

VDDA_PLL

VSSA_PLL

USBDP

USBDM

RX,TX

as AF

RX,TX,CTS,

RTS as AF

RX,TX,CTS,

RTS as AF

RX,TX,CTS,

RTS as AF

MOSI,MISO,

SCK,NSS

as AF

MOSI,MISO,

SCK,NSS

as AF

SCL,SDA

as AF

PWM TIMER

APB (up to 32 MHz)

AF: alternate function on I/O port pin

Note: I/Os shown for 100 pin devices. 64-pin devices have the I/O set shown in Figure 3.

11/84

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet STR755FR0.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| STR755FR0 | 32-bit MCU | STMicroelectronics |

| STR755FR1 | 32-bit MCU | STMicroelectronics |

| STR755FR2 | 32-bit MCU | STMicroelectronics |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |