|

|

PDF RS780 Data sheet ( Hoja de datos )

| Número de pieza | RS780 | |

| Descripción | Register Programming Requirements | |

| Fabricantes | AMD | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de RS780 (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

AMD 780G Family

Register Programming Requirements

For the RS780, RS780C, RS780D, RS780M,

RS780E, RS780MC, and RX781

Technical Reference Manual

Rev. 1.01

P/N: 43291_rs780_rpr_pub_1.01

© 2009 Advanced Micro Devices, Inc.

1 page

Table of Contents

5.10.14 Software Initiated Speed Change to GEN2 (CMOS Option – Disabled by Default).........................................5-49

5.10.15 Active State Power Management (ASPM).........................................................................................................5-51

5.10.16 Clock Gating.......................................................................................................................................................5-54

5.10.17 Non-Posted VC1 Traffic Support on SB Link (CMOS Option – Disabled by Default) ....................................5-55

5.11 Dynamic Link Width Control (CMOS Option – Disabled by Default) ..........................................................................5-56

5.12 PCI Enumeration and Special Features Programming Sequence ...................................................................................5-59

5.12.1 PCI Enumeration ................................................................................................................................................5-59

5.12.2 Program the Common Clock Configuration.......................................................................................................5-59

5.12.3 Slot Power Limit (CMOS Option - Default 75W) .............................................................................................5-59

5.12.4 Update Hot-Plug Info .........................................................................................................................................5-59

5.12.5 Disable Immediate Timeout on Link Down.......................................................................................................5-59

5.12.6 Register Locking ................................................................................................................................................5-60

5.12.7 Optional Features................................................................................................................................................5-60

5.12.8 Dynamic Link Width Control.............................................................................................................................5-60

5.12.9 Special Features Programming Sequence ..........................................................................................................5-60

Chapter 6: Graphics Core Settings

6.1 Bus Interface (BIF) .............................................................................................................................................................6-1

6.2 DEVICE_IDs, MAJOR_REV_IDs, MINOR_REV_IDs....................................................................................................6-1

6.3 CFG_ATI_REV_ID ............................................................................................................................................................6-1

6.4 GFX_DEBUG_BAR...........................................................................................................................................................6-1

6.5 Gpuioreg BAR For Accessing nbconfig Registers (A12)...................................................................................................6-2

6.6 Initialization ........................................................................................................................................................................6-2

6.7 Master Abort Status ............................................................................................................................................................6-3

6.8 HDP/MC Write Combiner ..................................................................................................................................................6-3

6.9 Graphics UMA FB Size ......................................................................................................................................................6-3

6.10 Suggested FB Interleaving Ratios.....................................................................................................................................6-4

Chapter 7: PCIE Initialization for DDI

7.1 PCIE Modes ........................................................................................................................................................................7-1

7.1.1 Case 1: PCIE 1x16 GFX.......................................................................................................................................7-1

7.1.2 Case 2: PCIE 1x8 GFX on Lanes 0-7...................................................................................................................7-1

7.1.3 Case 3: PCIE 1x8 GFX on Lanes 8-15.................................................................................................................7-2

7.1.4 Case 4: PCIE 2x8 .................................................................................................................................................7-3

7.1.5 Case 5: PCIE 1x4 GPP on Lanes 0-3 ..................................................................................................................7-3

7.1.6 Case 6: PCIE 1x4 GPP on Lanes 4-7 ..................................................................................................................7-3

7.1.7 Case 7: PCIE 1x4 GPP on Lanes 8-11 ................................................................................................................7-3

7.1.8 Case 8: PCIE 1x4 GPP on Lanes 12-15 ...............................................................................................................7-3

7.1.9 Case 9: PCIE 2x4 GPPs on Lanes 0-7..................................................................................................................7-4

7.1.10 Case 10: PCIE 1x4 GPP on Lanes 0-3 and 1x4 GPP on Lanes 8-11 ...................................................................7-5

7.1.11 Case 11: PCIE 1x4 GPP on Lanes 0-3 and 1x4 GPP on Lanes 12-15 .................................................................7-5

7.1.12 Case 12: PCIE 1x4 GPP on Lanes 4-7 and 1x8 GFX on Lanes 8-15...................................................................7-5

7.1.13 Case 13: PCIE 2x4 GPPs on Lanes 8-15..............................................................................................................7-5

7.1.14 Case 14: PCIE 1x8 GFX on Lanes 0-7 and 1x4 GPP on Lanes 8-11...................................................................7-7

7.1.15 Case 15: PCIE 1x8 GFX on Lanes 0-7 and 1x4 GPP on Lanes 12-15.................................................................7-7

7.1.16 Case 16: PCIE 1x8 GFX on Lanes 8-15 and 1x4 GPP on Lanes 4-7...................................................................7-9

7.1.17 Case 17: PCIE 1x4 GPP on Lanes 0-3 and 1x8 GFX on Lanes 8-15.................................................................7-10

7.2 DDI Modes........................................................................................................................................................................ 7-11

7.2.1 DDI Programming Sequence.............................................................................................................................. 7-11

7.2.2 Initialization Sequence .......................................................................................................................................7-14

7.2.3 Adjustable PHY Parameters for Better Quality Display ....................................................................................7-43

7.3 PCIE + DDI Modes...........................................................................................................................................................7-45

© 2009 Advanced Micro Devices, Inc.

AMD 780G Register Programming Requirements 1.01

Table of Contents-3

5 Page

Chapter 2

I/O Control (IOC)

2.1 RS780 Device Mapping

The RS780 has the following devices:

• Bus0Dev0Fun0: Host bridge

• Bus0Dev0Fun1: Clock control

• Bus0Dev1: Internal graphics P2P bridge

• Bus0Dev2: PCIE P2P bridge (external graphics)

• Bus0Dev3: PCIE P2P bridge (external graphics)

• Bus0Dev4: PCIE P2P bridge

• Bus0Dev5: PCIE P2P bridge

• Bus0Dev6: PCIE P2P bridge

• Bus0Dev7: PCIE P2P bridge

• Bus0Dev9: PCIE P2P bridge

• Bus0Dev10: PCIE P2P bridge

• Bus0Dev8: NB/SB Link P2P bridge (hidden by default)

Note: Each device has a P2P bridge header, except Dev0, which has a PCI device header.

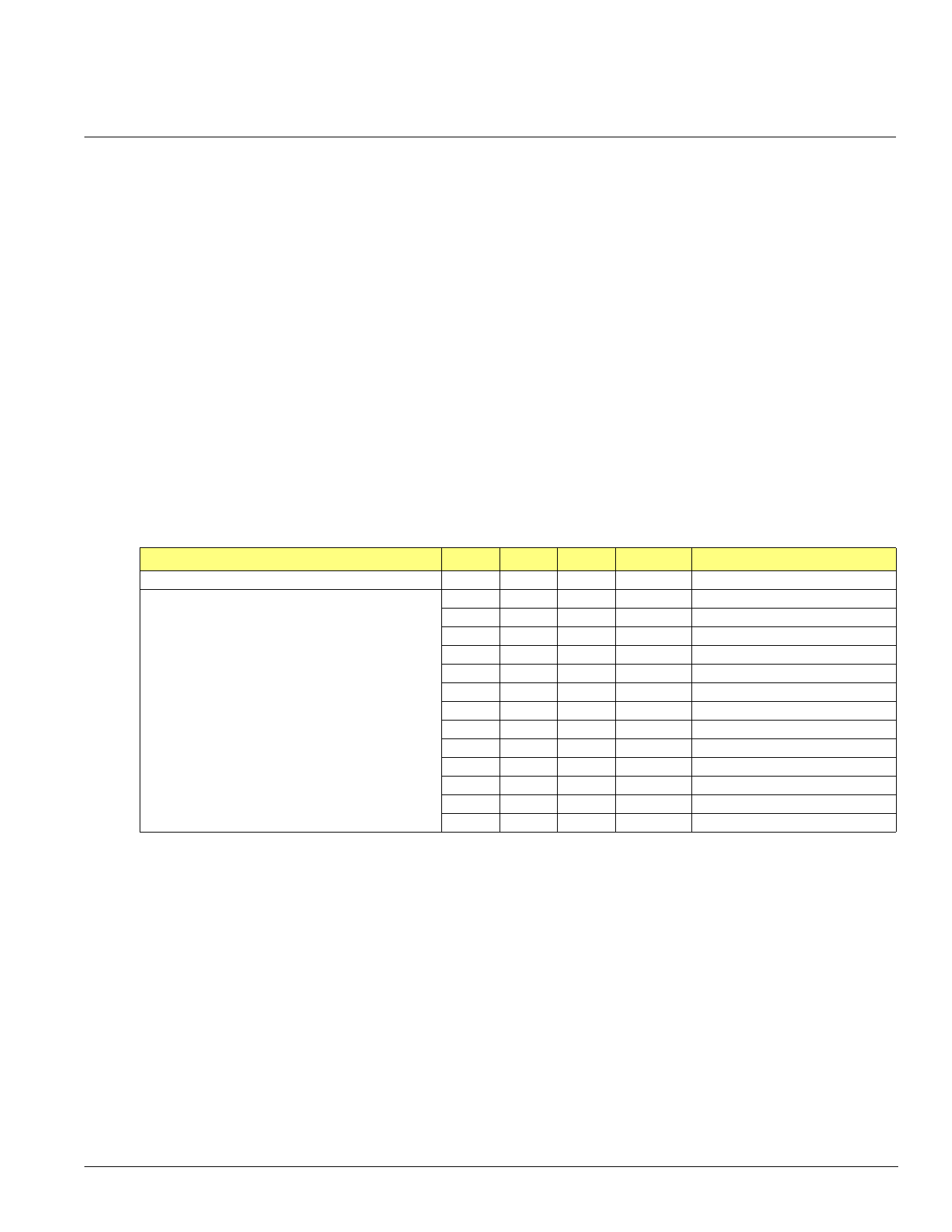

2.2 RS780 Device IDs

Table 2-1 RS780 Device IDs

Register

NB_DEVICE_ID<nbcfg:0X02>DEVICE_ID [15:0]

APC_DEVICE_ID<APCCFG:0x02>DEVICE_ID [15:0]

RS780

0x9600

0x9602

0x9603

0x960B

0x9610

0x9604

0x9605

0x9606

0x9607

0x9608

0x9609

0x960A

0x960F

0x791A

RS780C RS780M

0x9611 0x9612

RS780MC

Description

Northbridge configuration space ID

Internal PCI-PCI bridge ID

External GFX - port 0

External GFX - port 1

0x9613 Internal graphics

PCI-PCI bridge - Port 0

PCI-PCI bridge - Port 1

PCI-PCI bridge - Port 2

PCI-PCI bridge - Port 3

PCI-PCI bridge - Port 4

PCI-PCI bridge - Port 5

PCI-PCI bridge (SB)

HD Audio controller

HDMI Audio codec

© 2009 Advanced Micro Devices, Inc.

AMD 780G Register Programming Requirements 1.01

2-1

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet RS780.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| RS780 | Register Programming Requirements | AMD |

| RS780 | Register Programming Requirements | AMD |

| RS780C | Register Programming Requirements | AMD |

| RS780D | Register Programming Requirements | AMD |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |