|

|

PDF SPE0525S26RGB Data sheet ( Hoja de datos )

| Número de pieza | SPE0525S26RGB | |

| Descripción | 5-Line ESD Protection Array | |

| Fabricantes | SYNC POWER | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de SPE0525S26RGB (archivo pdf) en la parte inferior de esta página. Total 7 Páginas | ||

|

No Preview Available !

SPE0525

5-Line ESD Protection Array

DESCRIPTION

The SPE0525 are designed by TVS array that is to protect

sensitive electronics from damage or latch-up due to ESD.

They are designed for use in applications where board

space is at a premium. SPE0525 is bidirectional devices

that will protect up to five lines, and may be used on lines

where the signal polarities swing above and below

ground .

SPE0525 offer desirable characteristics for board level

protection including fast response time, low operating and

clamping voltage, and no device degradation.

SPE0525 may be used to meet the immunity requirements

of IEC 61000-4-2, level 4. The small SOT-23-6L package

makes them ideal for use in portable electronics such as

cell phones, PDA’s, notebook computers, and digital

cameras.

APPLICATIONS

Cellular Handsets and Accessories

Cordless Phone

PDA

Notebooks and Handhelds

Portable Instrumentation

Digital Cameras

MP3 Player

FEATURES

Transient protection for data lines to

IEC 61000-4-2 (ESD) ±15kV (air), ±8kV (contact)

IEC 61000-4-4 (EFT) 40A (5/50ns)

Protects five bidirectional I/O lines

Working voltage: 5V

Low leakage current

Low operating and clamping voltages

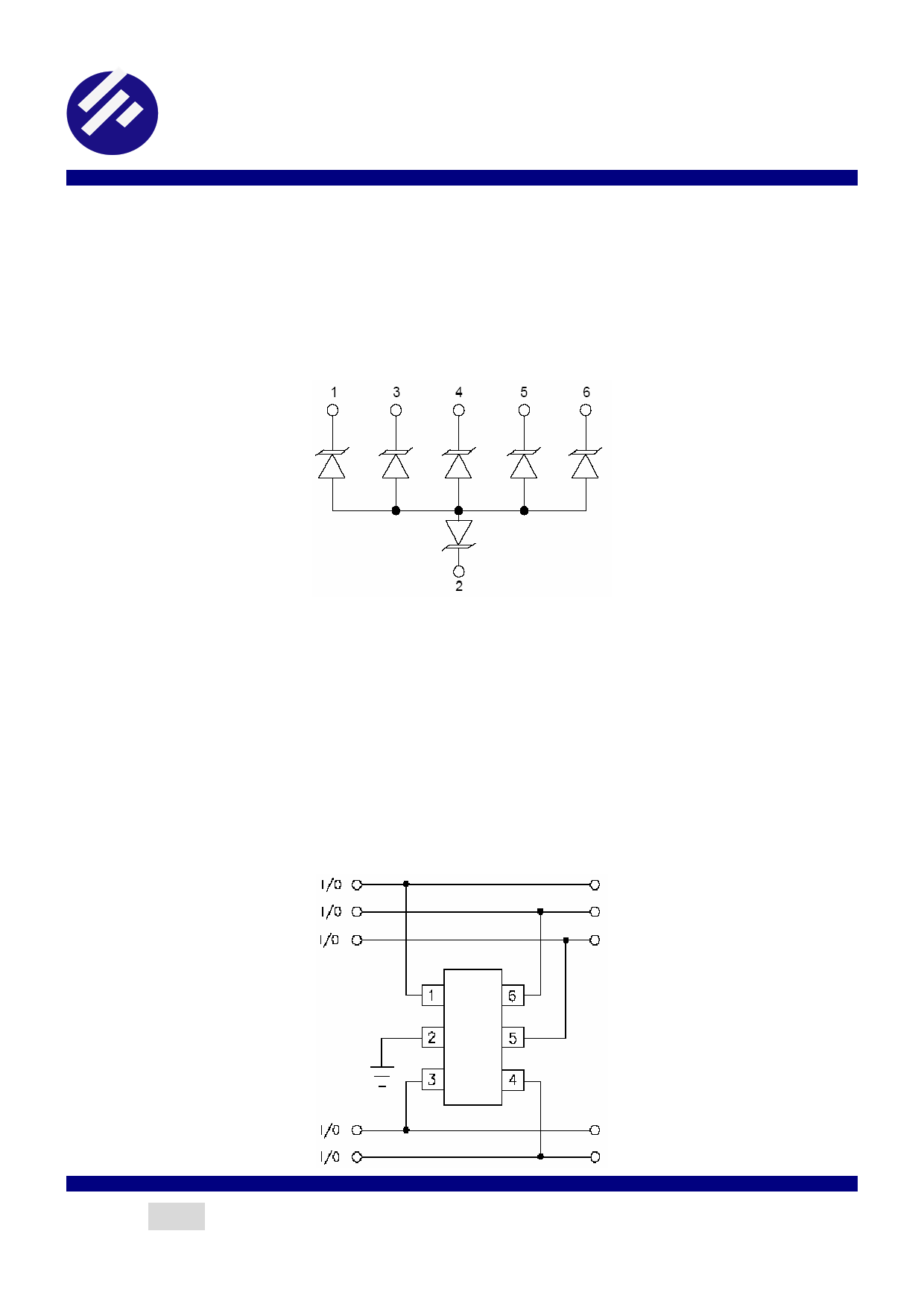

PIN CONFIGURATION ( SOT-23-6L )

PART MARKING

2009/01/10 Ver.1

Page 1

1 page

SPE0525

5-Line ESD Protection Array

APPLICATION NOTE

Device Connection for Protection of Five Data Lines

SPE0525 is designed to protect up to five bidirectional data lines. The device is connected as follows:

1. Bidirectional protection of five I/O lines is achieved by connecting pins 1, 3, 4, 5, and 6 to the data lines. Pin 2

is connected to ground. The ground connection should be made directly to the ground plane for best results.

The path length is kept as short as possible to reduce the effects of parasitic inductance in the board traces.

Circuit Board Layout Recommendations for Suppression of ESD

Good circuit board layout is critical for the suppression of ESD induced transients. The following guidelines are

recommended:

1. Place the TVS near the input terminals or connectors to restrict transient coupling.

2. Minimize the path length between the TVS and the protected line.

3. Minimize all conductive loops including power and ground loops.

4. The ESD transient return path to ground should be kept as short as possible.

5. Never run critical signals near board edges.

6. Use ground planes whenever possible.

2009/01/10 Ver.1

Page 5

5 Page | ||

| Páginas | Total 7 Páginas | |

| PDF Descargar | [ Datasheet SPE0525S26RGB.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| SPE0525S26RGB | 5-Line ESD Protection Array | SYNC POWER |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |