|

|

PDF HD61203UFS Data sheet ( Hoja de datos )

| Número de pieza | HD61203UFS | |

| Descripción | (Dot Matrix Liquid Crystal Graphic Display 64-Channel Common Driver) | |

| Fabricantes | Hitachi Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de HD61203UFS (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

HD61203U

(Dot Matrix Liquid Crystal Graphic Display

64-Channel Common Driver)

ADE-207-274(Z)

'99.9

Rev. 0.0

Description

The HD61203U is a common signal driver for dot matrix liquid crystal graphic display systems. It

generates the timing signals (switch signal to convert LCD waveform to AC, frame synchronous signal)

and supplies them to the column driver to control display. It provides 64 driver output lines and the

impedance is low enough to drive a large screen.

As the HD61203U is produced by a CMOS process, it is fit for use in portable battery-driven equipment

utilizing the liquid crystal display’s low power consumption. The user can easily construct a dot matrix

liquid crystal graphic display system by combining the HD61203U and the column (segment) driver

HD61202U.

Features

• Dot matrix liquid crystal graphic display common driver with low impedance

• Low impedance: 1.5 kΩ max

• Internal liquid crystal display driver circuit: 64 circuits

• Internal dynamic display timing generator circuit

• Display duty cycle

When used with the column driver HD61202U: 1/48, 1/64, 1/96, 1/128

When used with the controller HD61830: Selectable out of 1/32 to 1/128

• Low power dissipation: During displays: 5 mW

• Power supplies: VCC: 2.7~5.5V

• Power supply voltage for liquid crystal display drive: 8V to 16V

• CMOS process

• 100-pin plastic QFP, 100-pin plastic TQFP, chip

1

1 page

HD61203U

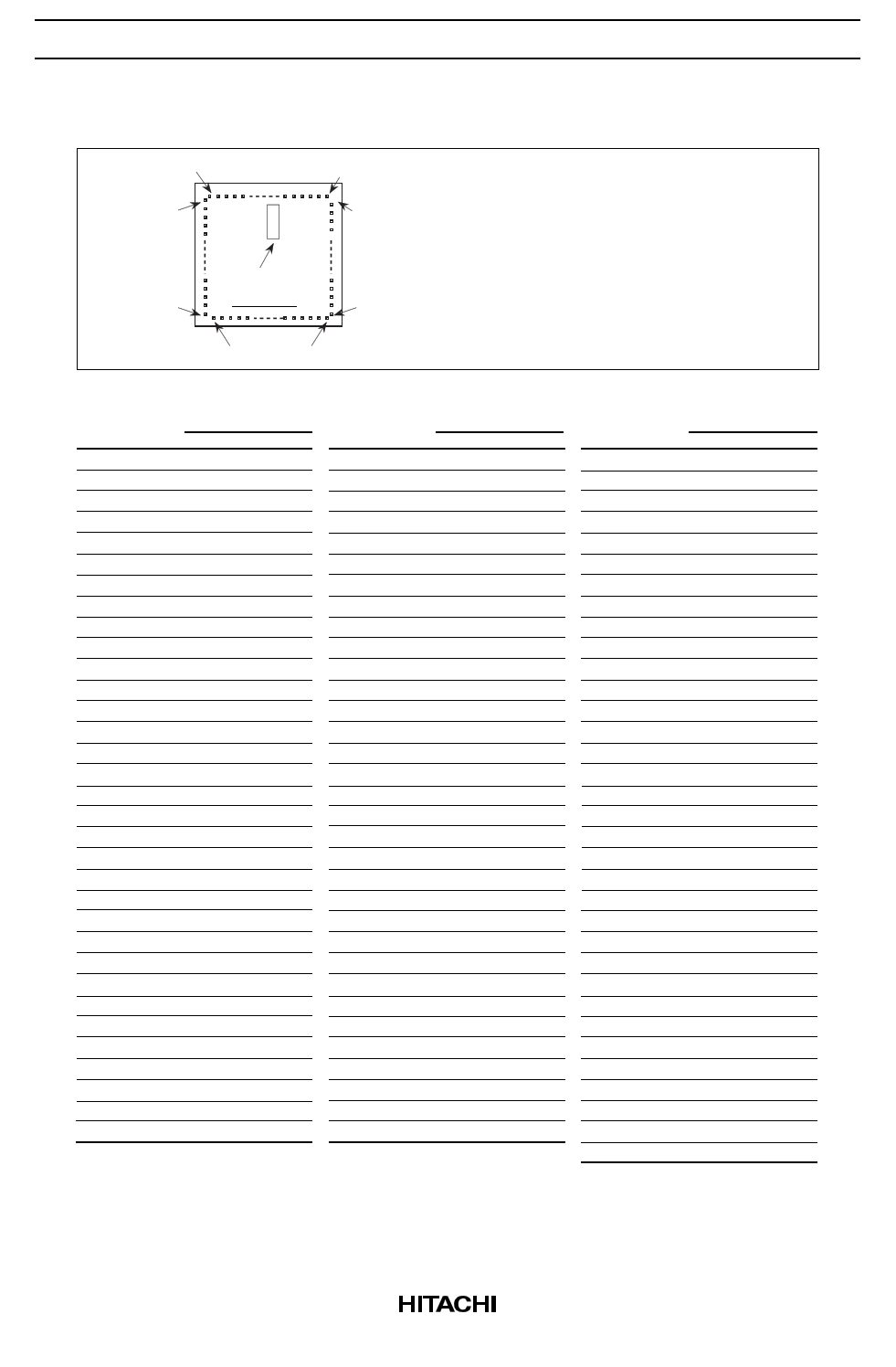

Pad Arrangement

No.1

NO.79

NO.2

NO.78

NO.28

TYPE CODE

HD61203U

NO.54

Chip Size

Coordinate

Origin

Pad Size

: 3.40 × 4.08 µm2

: Pad Center

: Chip center

: 90 × 90 µm2

No.29

No.52

Pad Location Coordinates

PAD PAD

No. Name

1 X22

2 X21

3 X20

4 X19

5 X18

6 X17

7 X16

8 X15

9 X14

10 X13

11 X12

12 X11

13 X10

14 X9

15 X8

16 X7

17 X6

18 X5

19 X4

20 X3

21 X2

22 X1

23 VEE1

24 V6L

25 V5L

26 V2L

27 V1L

28 VCC

29 DL

30 FS

31 DS1

32 DS2

33 C

Coordinate

XY

–1479

1853

–1513

1712

–1513

1544

–1513

1385

–1513

1238

–1513

1091

–1513

952

–1513

822

–1513

692

–1513

562

–1513

432

–1513

302

–1513

172

–1513

–1513

42

–88

–1513

–1513

–218

–349

–1513

–479

–1513

–609

–1513

–739

–1513

–869

–1513

–999

–1513 –1129

–1513 –1259

–1513 –1389

–1513 –1527

–1513 –1665

–1513 –1821

–1375 –1853

–1213 –1853

–976 –1828

–846 –1828

–716 –1828

PAD

No.

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

53

54

55

56

57

58

59

60

61

62

63

64

65

66

PAD

Name

R

CR

SHL

GND

M/S

PHI2

PHI1

FRM

M

FCS

DR

CL2

V1R

V2R

V5R

V6R

VEE2

X64

X63

X62

X61

X60

X59

X58

X57

Coordinate

XY

–586 –1828

–456 –1828

–196

–65

–1828

–1828

65 –1828

195 –1828

325 –1828

455 –1828

585 –1828

715 –1828

853 –1828

1407 –1828

1513

1513

1513

1513

1513

1513

1513

1513

1513

1513

1513

1513

1513

–1522

–1374

–1236

–1097

–967

–837

–707

–577

–447

–317

–187

–57

73

PAD PAD

No. Name

67 X56

68 X55

69 X54

70 X53

71 X52

72 X51

73 X50

74 X49

75 X48

76 X47

77 X46

78 X45

79 X44

80 X43

81 X42

82 X41

83 X40

84 X39

85 X38

86 X37

87 X36

88 X35

89 X34

90 X33

91 X32

92 X31

93 X30

94 X29

95 X28

96 X27

97 X26

98 X25

99 X24

100 X23

Coordinate

XY

1513

203

1513

333

1513

463

1513

593

1513

723

1513

853

1513

983

1513 1122

1513 1261

1513 1399

1513 1546

1513

1470

1693

1853

1304

1853

1170

1853

1040

1853

910 1853

779 1853

649 1853

519 1853

389 1853

259 1853

129 1853

–1

–131

1853

1853

–261

1853

–391

1853

–521

1853

–651

1853

–781

1853

–911

1853

–1041

1853

–1171

1853

–1301

1853

5

5 Page

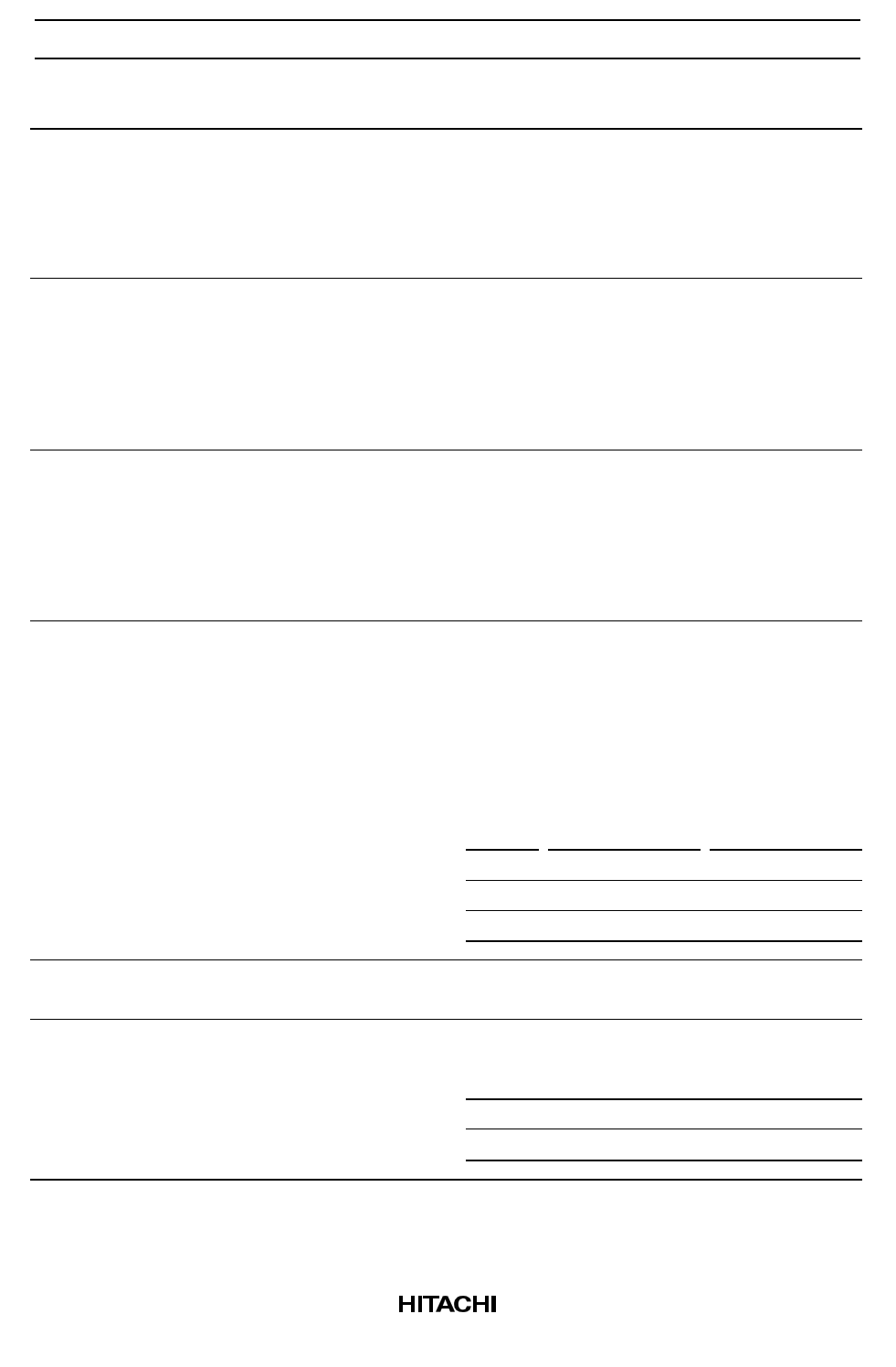

Terminal

Name

FRM

M

CL2

DL, DR

NC

SHL

Number of

Terminals

1

1

1

2

5

1

HD61203U

I/O Connected to Functions

O HD61202U Frame signal

• Master mode

Connect this terminal to terminal FRM of the

HD61202U.

• Slave mode

Don’t connect any lines to this terminal.

I/O MB of

Signal to convert LCD driver signal into AC

HD61830 or M • Master mode: Output terminal

of HD61202U

Connect this terminal to terminal M of the

HD61202U.

• Slave mode: Input terminal

Connect this terminal to terminal MB of the

HD61830.

I/O CL1 or MA of Shift clock

HD61830 or

CL of

HD61202U

• Master mode: Output terminal

Connect this terminal to terminal CL of the

HD61202U.

• Slave mode: Input terminal

Connect this terminal to terminal CL1 or MA of

the HD61830.

I/O Open or FLM Data I/O terminals of bidirectional shift register

of HD61830 DL corresponds to X1’s side and DR to X64’s side.

• Master mode

Output common scanning signal. Don’t connect

any lines to these terminals normally.

• Slave mode

Connect terminal FLM of the HD61830 to DL

(when SHL = VCC) or DR (when SHL = GND).

M/S

VCC

GND

SHL

VCC

GND

VCC

GND

DL Output Output Input Output

DR Output Output Output Input

Open

Not used.

Don’t connect any lines to this terminal.

I VCC or GND Selects shift direction of bidirectional shift register.

Common

SHL Shift Direction

Scanning Direction

VCC

GND

DL → DR

DL ← DR

X1 → X64

X1 ← X64

11

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet HD61203UFS.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| HD61203UFS | (Dot Matrix Liquid Crystal Graphic Display 64-Channel Common Driver) | Hitachi Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |