|

|

PDF AK1544 Data sheet ( Hoja de datos )

| Número de pieza | AK1544 | |

| Descripción | 1300MHz Integer-N Frequency Synthesizer | |

| Fabricantes | AKM | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de AK1544 (archivo pdf) en la parte inferior de esta página. Total 37 Páginas | ||

|

No Preview Available !

[AK1544]

AK1544

1300MHz Integer-N Frequency Synthesizer

1. Overview

Consisting a highly accurate charge pump that supports current adjustment in 9 steps, a reference divider, a

programmable divider and a dual-modulus prescaler (P/P+1), the AK1544 provides high performance, low consumption

current and small footprint for a wide range of frequency conversions. This synthesizer also has two general-purpose

output pins which allow it to be used to control the RF front end.

An ideal Phase Locked Loop (PLL) can be achieved by combining the AK1544 with the external loop filter and VCO

(Voltage Controlled Oscillator). Access to the registers is controlled via a 3-wire serial interface. The operating supply

voltage is from 2.7V to 5.5V; and the supply voltage for the charge pump and that for the serial interface can be driven

separately.

2. Features

Operating frequency:

400 to 1300MHz

Programmable charge pump current:

160 to 2530A typical

The charge pump current can be changed in 9 steps, and the

current range can be adjusted by the external resistance.

Two current settings can be specified with the register and switched

over from one to another using the timer.

Supply Voltage:

2.7 to 5.5 V (PVDD pin)

Separate power supply for the charge pump: PVDD to 5.5V (CPVDD pin)

On-chip power-saving features

On-chip lock detection feature of PLL:

Direct output to the PFD (Phase frequency detector)

or digital filtering output can be selected.

General-purpose output:

It has two general-purpose output ports to control peripheral

parts.

Very low consumption current:

2.8mA typical

Package:

24pin QFN (0.5mm pitch, 4mm4mm0.7mm)

Operating temperature:

-40°C to 85°C

MS1350-E-01

1

2013/03

http://www.Datasheet4U.com

1 page

[AK1544]

Note 1)

Note 2)

For detailed functional descriptions, see the section “Charge Pump and Loop Filter” in “8. Block Functional

Description” below.

The input voltage from the [CPZ] pin is used in the internal circuit. The [CPZ] pin must not be open even

when the fast lockup feature is unused. For the output destination from the [CPZ] pin, see

“P.12 Fig.5 Loop Filter Schematic”. The [SWIN] pin could be open even when the first lockup feature is not

Note 3)

Note 4)

used.

The switch for Loop Filter setting is ON when “PDN1=0, PDN2=0” or “PDN1=1, PDN2=”.

Power down refers to the state where [PDN1]=[PDN2]=”Low” after power-on.

AI: Analog input pin

DO: igital output pin

AO: Analog output pin

P: Power supply pin

AIO: Analog I/O pin

G: Ground pin

DI: Digital input pin

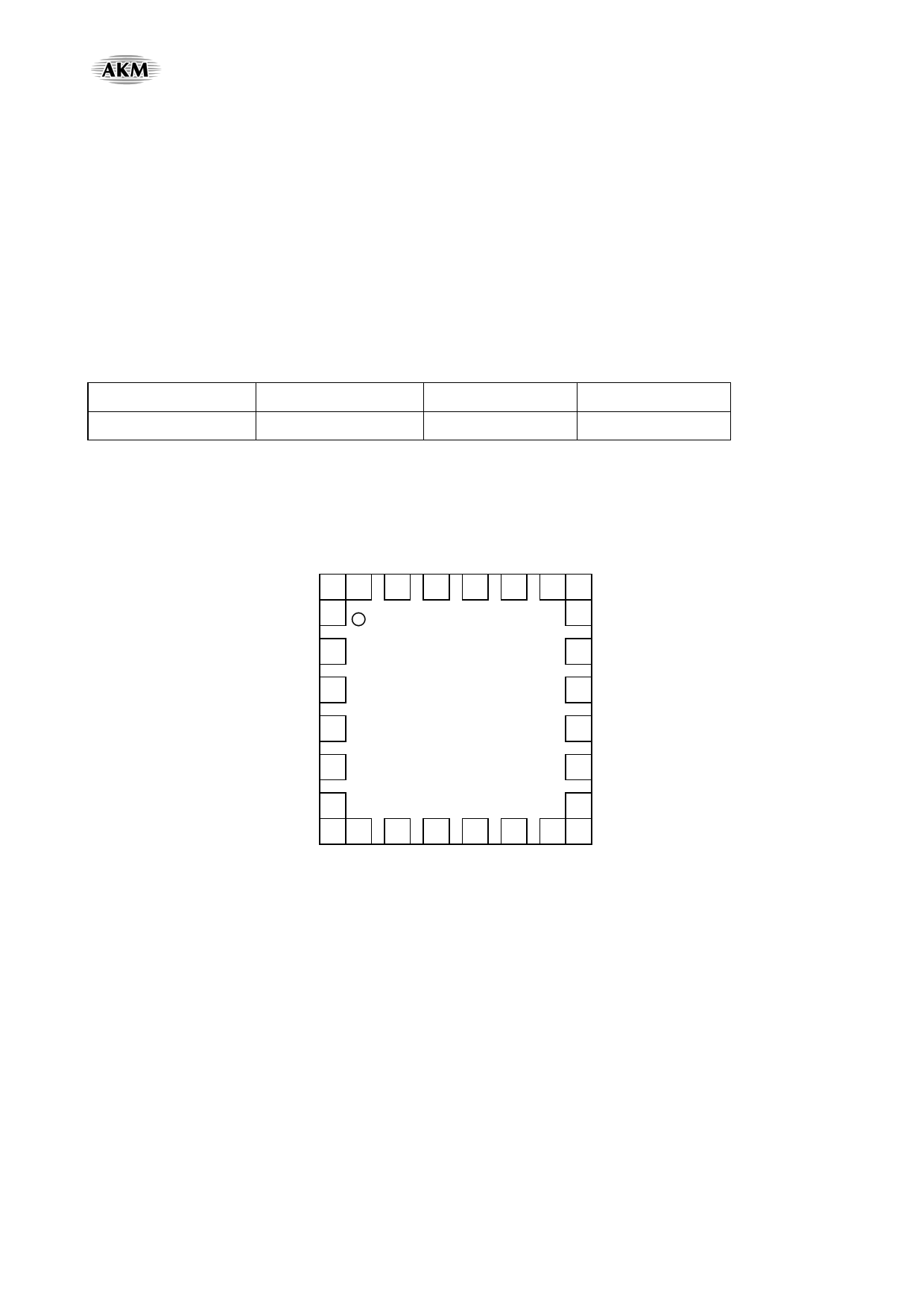

24 23 22 21 20 19

CPVDD 1

18 PVDD

TEST3 2

17 RFINP

TEST1 3

LE 4

TOP

VIEW

16 RFINN

15 VREF

DATA 5

14 DVSS

CLK 6

13 GPO2

7 8 9 10 11 12

Fig. 2 Package Pin Layout

MS1350-E-01

5

2013/03

5 Page

[AK1544]

8. Block Functional Descriptions

1. Frequency Setup

The following formula is used to calculate the frequency setting for the AK1544.

Frequency setting (external VCO output frequency) = FPFD x N

N

FPFD

P

B

A

: Dividing number N = [ (P x B) + A ]

: Phase detector frequency FPFD = [REFIN] pin input frequency / R counter dividing number

: Prescaler Value (See< Address2>:{Pre[1:0]})

: B (Programmable) counter value (See <Address1>:{B[12:0]})

: A (Swallow) counter value (See <Address1>:{A[5:0]})

○ Calculation examples

When the [REFIN] pin input frequency is 10MHz, the phase detector frequency FPFD =5kHz and the frequency setting

= 780.1MHz;

[The AK1544 Settings]

R=10000000/5000 = 2000 (<Address3> : {R[13:0]}=2000dec)

P=32 (<Address2> : Pre[1:0]=10bin)

B=4875 (<Address1> : B[12:0]=4875dec)

A=20 (<Address1> : A[5:0]=20dec)

Frequency setting= 5000 × [ (32×4875) + 20] = 780.1MHz

○ Division conditions

The conditions for division settings for A and B counters are as follows:

A ≥ 0 A counter (6 bits): A decimal number from 0 to 63 can be set.

B ≥ 3 B counter (13 bits): A decimal number from 3 to 8191 can be set.

B≥A

○ Lower limit for setting consecutive dividing numbers

In the AK1544, it is not possible to set consecutive dividing numbers below the lower limit.

The lower limit can be calculated by the following formula;

Nmin=P2-P

For example, in the case of P=16, 240 or over can be set as consecutive dividing number.

MS1350-E-01

11

2013/03

11 Page | ||

| Páginas | Total 37 Páginas | |

| PDF Descargar | [ Datasheet AK1544.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| AK1541 | 20 to 600MHz Delta-Sigma Fractional-N Frequency Synthesizer | AKM |

| AK1542A | 20 to 600MHz Integer-N Frequency Synthesizer | AKM |

| AK1543 | 1300MHz Delta-Sigma Fractional-N Frequency Synthesizer | AKM |

| AK1544 | 1300MHz Integer-N Frequency Synthesizer | AKM |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |