|

|

PDF F25L32QA-86PHG Data sheet ( Hoja de datos )

| Número de pieza | F25L32QA-86PHG | |

| Descripción | 3V Only 32 Mbit Serial Flash Memory | |

| Fabricantes | ESMT | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de F25L32QA-86PHG (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

ESMT

Flash

FEATURES

y Single supply voltage 2.7~3.6V

y Standard, Dual and Quad SPI

y Speed

- Read max frequency: 33MHz

- Fast Read max frequency: 50MHz / 86MHz / 100MHz

- Fast Read Dual/Quad max frequency: 50MHz / 86MHz /

100MHz

(100MHz / 172MHz / 200MHz equivalent Dual SPI;

200MHz / 344MHz / 400MHz equivalent Quad SPI)

y Low power consumption

- Active current: 35 mA

- Standby current: 30 μ A

- Deep Power Down current: 5 μ A

y Reliability

- 100,000 typical program/erase cycles

- 20 years Data Retention

y Program

- Byte programming time: 7 μ s (typical)

- Page programming time: 1.5 ms (typical)

F25L32QA

3V Only 32 Mbit Serial Flash Memory

with Dual and Quad

y Erase

- Chip erase time 25 sec (typical)

- Block erase time 1 sec (typical)

- Sector erase time 90 ms (typical)

y Page Programming

- 256 byte per programmable page

y Lockable 512 bytes OTP security sector

y SPI Serial Interface

- SPI Compatible: Mode 0 and Mode 3

y End of program or erase detection

y Write Protect ( WP )

y Hold Pin ( HOLD )

y All Pb-free products are RoHS-Compliant

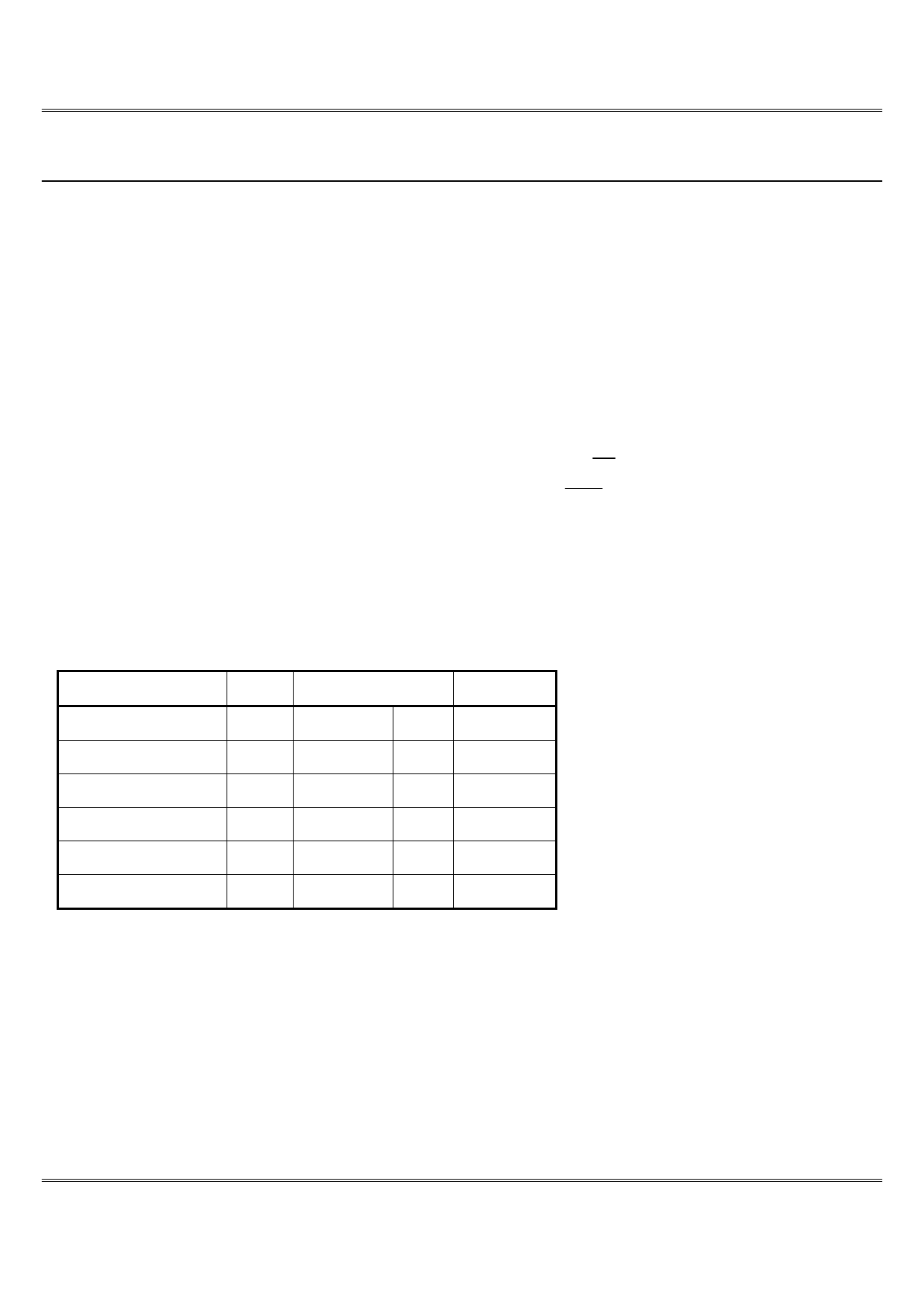

ORDERING INFORMATION

Product ID

Speed

Package

F25L32QA –50PAG

50MHz 8 lead SOIC 200mil

F25L32QA –86PAG

86MHz 8 lead SOIC 200mil

F25L32QA –100PAG 100MHz 8 lead SOIC 200mil

F25L32QA –50PHG

50MHz 16 lead SOIC 300mil

F25L32QA –86PHG

86MHz 16 lead SOIC 300mil

F25L32QA –100PHG 100MHz 16 lead SOIC 300mil

Comments

Pb-free

Pb-free

Pb-free

Pb-free

Pb-free

Pb-free

GENERAL DESCRIPTION

The F25L32QA is a 32Megabit, 3V only CMOS Serial Flash

memory device. The device supports the standard Serial

Peripheral Interface (SPI), and a Dual/Quad SPI. ESMT’s

memory devices reliably store memory data even after 100,000

programming and erase cycles.

The memory array can be organized into 16,384 programmable

pages of 256 byte each. 1 to 256 byte can be programmed at a

time with the Page Program instruction.

Elite Semiconductor Memory Technology Inc.

The device features sector erase architecture. The memory array

is divided into 1024 uniform sectors with 4K byte each; 64

uniform blocks with 64K byte each. Sectors can be erased

individually without affecting the data in other sectors. Blocks can

be erased individually without affecting the data in other blocks.

Whole chip erase capabilities provide the flexibility to revise the

data in the device. The device has Sector, Block or Chip Erase

but no page erase.

The sector protect/unprotect feature disables both program and

erase operations in any combination of the sectors of the

memory.

Publication Date: Jan. 2010

Revision: 1.1

1/40

Free Datasheet http://www.Datasheet4U.com

1 page

ESMT

F25L32QA

Block

50

49

48

47

46

45

44

43

42

41

40

39

38

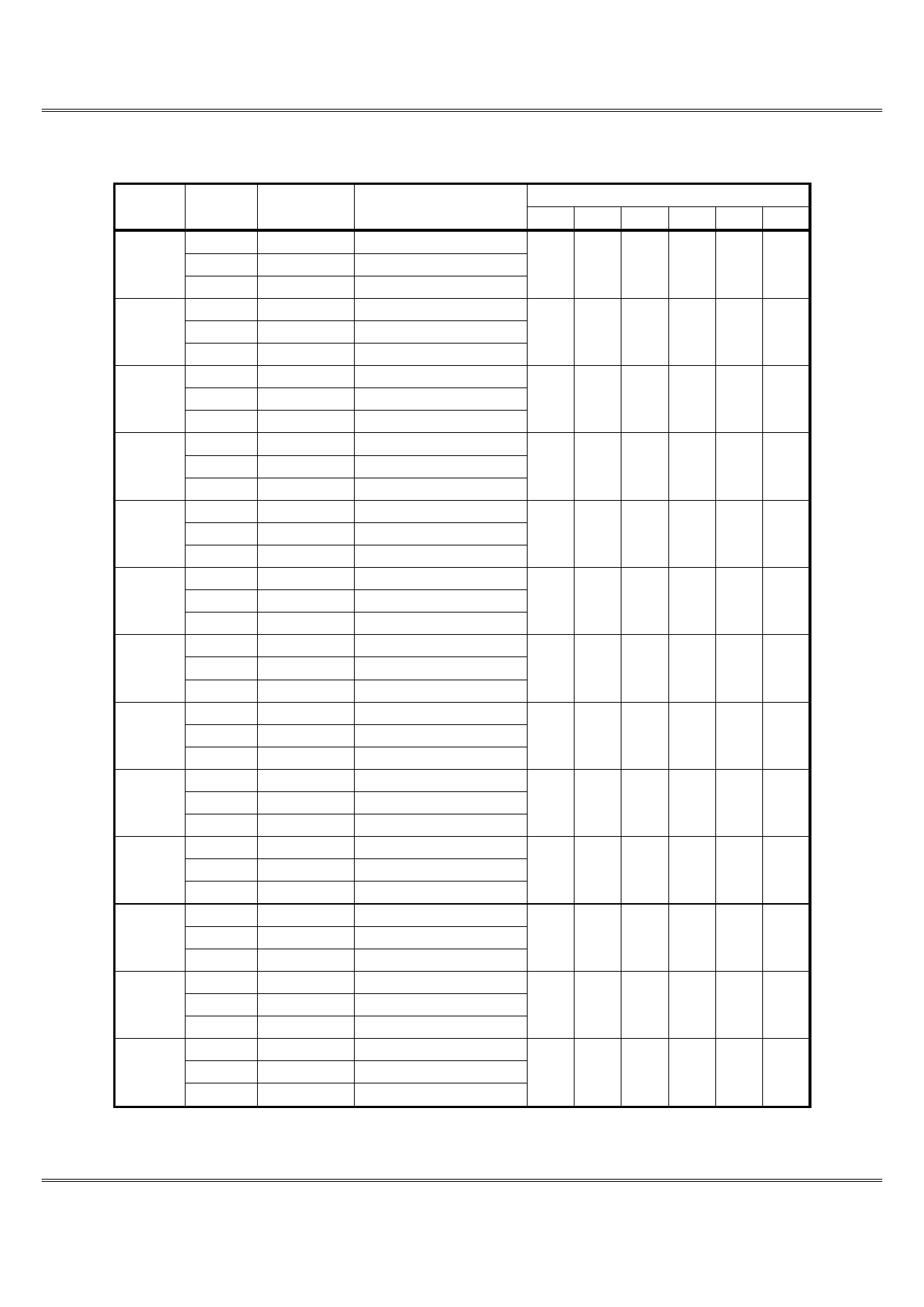

Table 1: F25L32QA Sector Address Table – Continued I

Sector

815

:

800

799

:

784

783

:

768

767

:

752

751

:

736

735

:

720

719

:

704

703

:

688

687

:

672

671

:

656

655

:

640

639

:

624

623

:

608

Sector Size

(Kbytes)

4KB

:

4KB

4KB

:

4KB

4KB

:

4KB

4KB

:

4KB

4KB

:

4KB

4KB

:

4KB

4KB

:

4KB

4KB

:

4KB

4KB

:

4KB

4KB

:

4KB

4KB

:

4KB

4KB

:

4KB

4KB

:

4KB

Address range

32F000H – 32FFFFH

:

320000H – 320FFFH

31F000H – 31FFFFH

:

310000H – 310FFFH

30F000H – 30FFFFH

:

300000H – 300FFFH

2FF000H – 2FFFFFH

:

2F0000H – 2F0FFFH

2EF000H – 2EFFFFH

:

2E0000H – 2E0FFFH

2DF000H – 2DFFFFH

:

2D0000H – 2D0FFFH

2CF000H – 2CFFFFH

:

2C0000H – 2C0FFFH

2BF000H – 2BFFFFH

:

2B0000H – 2B0FFFH

2AF000H – 2AFFFFH

:

2A0000H – 2A0FFFH

29F000H – 29FFFFH

:

290000H – 290FFFH

28F000H – 28FFFFH

:

280000H – 280FFFH

27F000H – 27FFFFH

:

270000H – 270FFFH

26F000H – 26FFFFH

:

260000H – 260FFFH

Block Address

A21 A20 A19 A18 A17 A16

110010

110001

110000

101111

101110

101101

101100

101011

101010

101001

101000

100111

100110

Elite Semiconductor Memory Technology Inc.

Publication Date: Jan. 2010

Revision: 1.1

5/40

Free Datasheet http://www.Datasheet4U.com

5 Page

ESMT

F25L32QA

HOLD OPERATION

HOLD pin is used to pause a serial sequence underway with the

SPI flash memory without resetting the clocking sequence. To

activate the HOLD mode, CE must be in active low state. The

HOLD mode begins when the SCK active low state coincides

with the falling edge of the HOLD signal. The HOLD mode ends

when the HOLD signal’s rising edge coincides with the SCK

active low state.

If the falling edge of the HOLD signal does not coincide with the

SCK active low state, then the device enters Hold mode when the

SCK next reaches the active low state.

Similarly, if the rising edge of the HOLD signal does not

coincide with the SCK active low state, then the device exits in

Hold mode when the SCK next reaches the active low state. See

Figure 1 for Hold Condition waveform.

Once the device enters Hold mode, SO will be in high impedance

state while SI and SCK can be VIL or VIH.

If CE is driven active high during a Hold condition, it resets the

internal logic of the device. As long as HOLD signal is low, the

memory remains in the Hold condition. To resume

communication with the device, HOLD must be driven active

high, and CE must be driven active low. See Figure 23 for Hold

timing.

The HOLD function is only available for Standard SPI and Dual

SPI operation, not during Quad SPI because this pin is used for

SIO3 when the QE bit of Status Register-2 is set for Quad I/O.

SCK

HOLD

A ctive

Figure 1: HOLD Condition Waveform

Ho ld

A ctive

Ho ld

A ctive

WRITE PROTECTION

F25L32QA provides software Write Protection.

The Write-Protect pin ( WP ) enables or disables the lock-down

function of the status register. The Block-Protection bits (BP2,

BP1, BP0, and BPL) in the status register provide Write

protection to the memory array and the status register. When the

QE bit of Status Register-2 is set for Quad I/O, the WP pin

function is not available since this pin is used for SIO2. See Table

3 for Block-Protection description.

Write Protect Pin ( WP )

The Write-Protect ( WP ) pin enables the lock-down function of

the BPL bit (bit 7) in the status register. When WP is driven low,

the execution of the Write Status Register (WRSR) instruction is

determined by the value of the BPL bit (see Table 4). When WP

is high, the lock-down function of the BPL bit is disabled.

Table 4: Conditions to Execute Write-Status- Register

(WRSR) Instruction

WP BPL Execute WRSR Instruction

L1

Not Allowed

L0

Allowed

HX

Allowed

Elite Semiconductor Memory Technology Inc.

Publication Date: Jan. 2010

Revision: 1.1

11/40

Free Datasheet http://www.Datasheet4U.com

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet F25L32QA-86PHG.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| F25L32QA-86PHG | 3V Only 32 Mbit Serial Flash Memory | ESMT |

| F25L32QA-86PHG2S | 32 Mbit Serial Flash Memory | ESMT |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |