|

|

PDF H5TQ4G63MFR-xxJ Data sheet ( Hoja de datos )

| Número de pieza | H5TQ4G63MFR-xxJ | |

| Descripción | 4Gb DDR3 SDRAM | |

| Fabricantes | Hynix | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de H5TQ4G63MFR-xxJ (archivo pdf) en la parte inferior de esta página. Total 30 Páginas | ||

|

No Preview Available !

4Gb DDR3 SDRAM

4Gb DDR3 SDRAM

Lead-Free&Halogen-Free

(RoHS Compliant)

H5TQ4G83MFR-xxC

H5TQ4G83MFR-xxI

H5TQ4G83MFR-xxJ

H5TQ4G63MFR-xxC

H5TQ4G63MFR-xxI

H5TQ4G63MFR-xxJ

* Hynix Semiconductor reserves the right to change products or specifications without notice.

Rev. 1.0/ Feb. 2012

1

Free Datasheet http://www.datasheet4u.com/

1 page

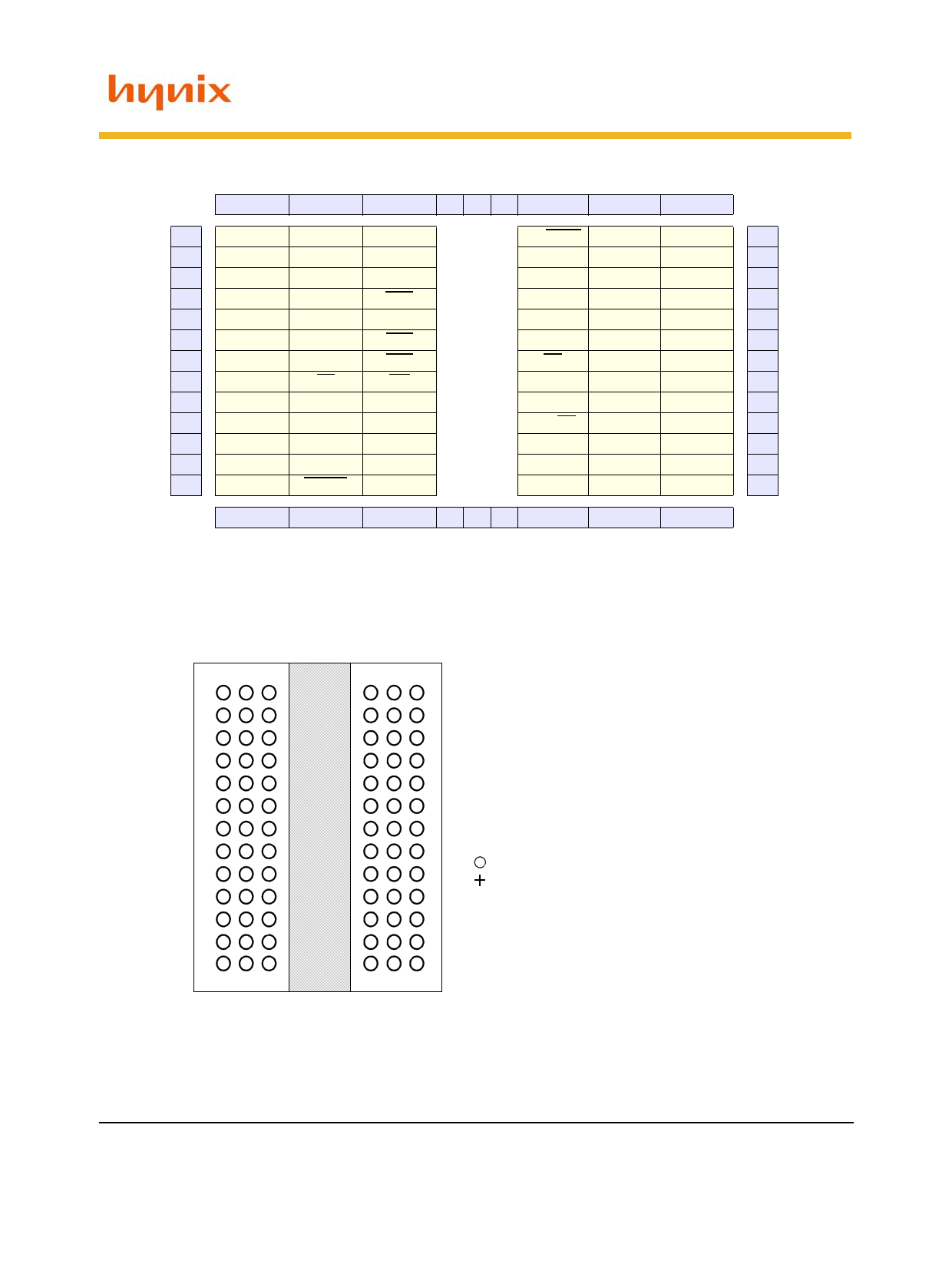

x8 Package Ball out (Top view): 78ball FBGA Package

12

A VSS VDD

B

VSS

VSSQ

C VDDQ DQ2

D VSSQ DQ6

E VREFDQ VDDQ

F NC VSS

G ODT VDD

H NC

CS

J VSS BA0

K VDD

A3

L VSS

A5

M VDD

A7

N

VSS

RESET

12

3

NC

DQ0

DQS

DQS

DQ4

RAS

CAS

WE

BA2

A0

A2

A9

A13

3

456

7

8

NF/TDQS

DM/TDQS

DQ1

VDD

DQ7

CK

CK

A10/AP

A15

A12/BC

A1

A11

A14

VSS

VSSQ

DQ3

VSS

DQ5

VSS

VDD

ZQ

VREFCA

BA1

A4

A6

A8

456

7

8

9

VDD

VDDQ

VSSQ

VSSQ

VDDQ

NC

CKE

NC

VSS

VDD

VSS

VDD

VSS

9

A

B

C

D

E

F

G

H

J

K

L

M

N

1 23

A

B

C

D

E

F

G

H

J

K

L

M

N

7 89

(Top View: See the balls through the Package)

Populated ball

Ball not populated

Rev. 1.0/ Feb. 2012

5

Free Datasheet http://www.datasheet4u.com/

5 Page

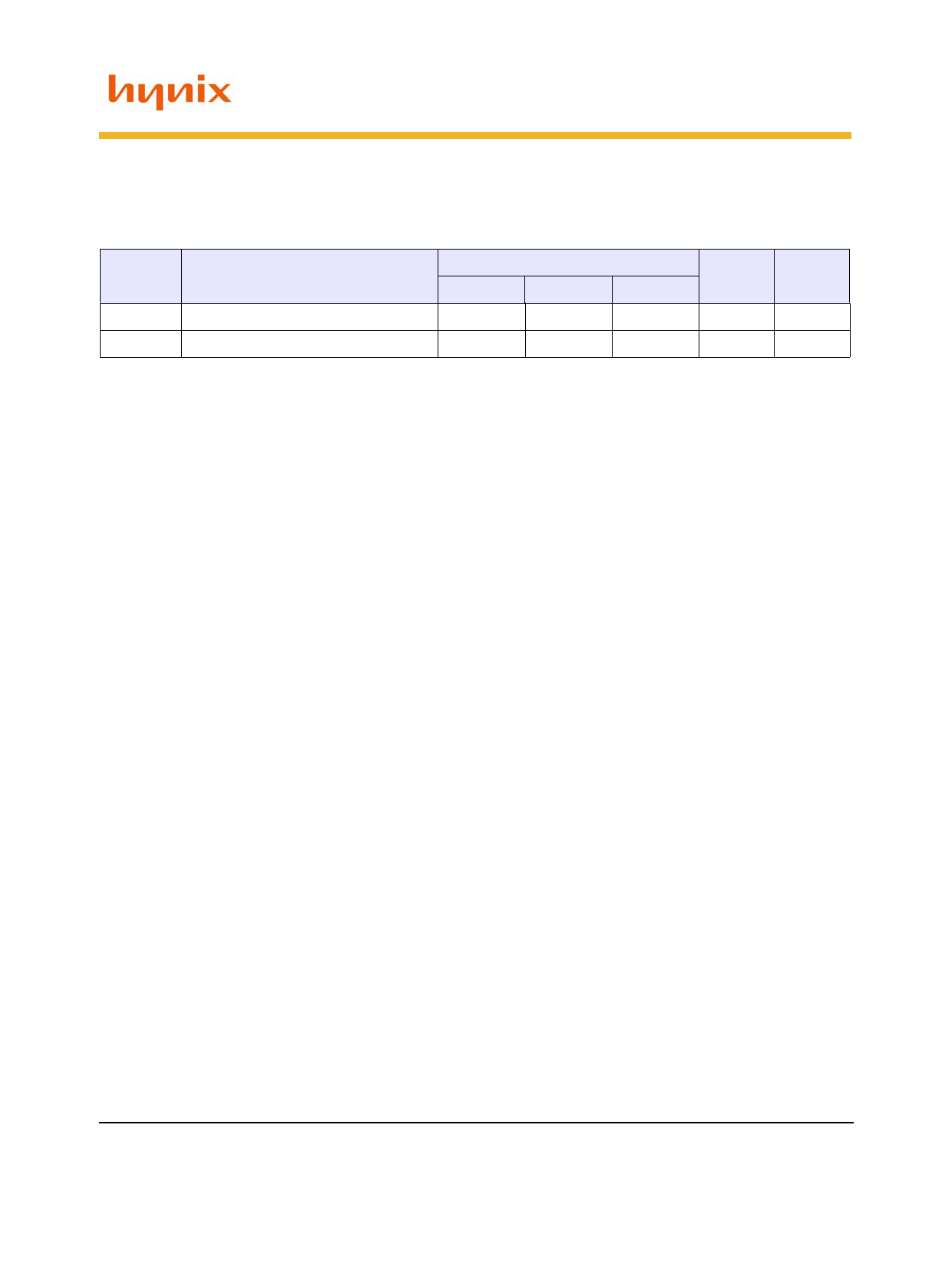

AC & DC Operating Conditions

Recommended DC Operating Conditions

Recommended DC Operating Conditions

Symbol

Parameter

VDD

VDDQ

Notes:

Supply Voltage

Supply Voltage for Output

Min.

1.425

1.425

Rating

Typ.

1.500

1.500

Max.

1.575

1.575

1. Under all conditions, VDDQ must be less than or equal to VDD.

2. VDDQ tracks with VDD. AC parameters are measured with VDD and VDDQ tied together.

Units

V

V

Notes

1,2

1,2

Rev. 1.0/ Feb. 2012

11

Free Datasheet http://www.datasheet4u.com/

11 Page | ||

| Páginas | Total 30 Páginas | |

| PDF Descargar | [ Datasheet H5TQ4G63MFR-xxJ.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| H5TQ4G63MFR-xxC | 4Gb DDR3 SDRAM | Hynix Semiconductor |

| H5TQ4G63MFR-xxC | 4Gb DDR3 SDRAM | Hynix |

| H5TQ4G63MFR-xxI | 4Gb DDR3 SDRAM | Hynix |

| H5TQ4G63MFR-xxJ | 4Gb DDR3 SDRAM | Hynix |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |