|

|

PDF MT16LSDT6464A Data sheet ( Hoja de datos )

| Número de pieza | MT16LSDT6464A | |

| Descripción | SYNCHRONOUS DRAM MODULE | |

| Fabricantes | Micron Technology | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MT16LSDT6464A (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

SYNCHRONOUS

DRAM MODULE

256MB / 512MB (x64)

168-PIN SDRAM DIMMs

MT8LSDT3264A(I) - 256MB

MT16LSDT6464A(I) - 512MB

For the latest data sheet, please refer to the Micron Web

site: www.micron.com/moduleds

Features

• PC100- and PC133-compliant

• JEDEC-standard 168-pin, dual in-line memory

module (DIMM)

• Unbuffered

• 256MB (32 Meg x 64), 512MB (64 Meg x 64)

• Single +3.3V ±0.3V power supply

• Fully synchronous; all signals registered on positive

edge of system clock

• Internal pipelined operation; column address can

be changed every clock cycle

• Internal SDRAM banks for hiding row access/precharge

• Programmable burst lengths: 1, 2, 4, 8, or full page

• Auto Precharge, including Concurrent Auto

Precharge, and Auto Refresh Modes

• 64ms, 8,192 cycle Auto Refresh cycle

• Self Refresh Mode

• LVTTL-compatible inputs and outputs

• Serial Presence-Detect (SPD)

OPTIONS

MARKING

• Package

Unbuffered

168-pin DIMM (gold)

• Operating Temperature Range

Commercial (0°C to +70°C)

Industrial (-40°C to +85°C)1

• Memory Clock/CAS Latency

(133 MHz)/CL = 2

(133 MHz)/CL = 3

(100 MHz)/CL = 2

A

G

None

I

-13E

-133

-10E

NOTE:

1. Consult Micron for availability; Industrial Tempera-

ture Option available in -133 speed only.

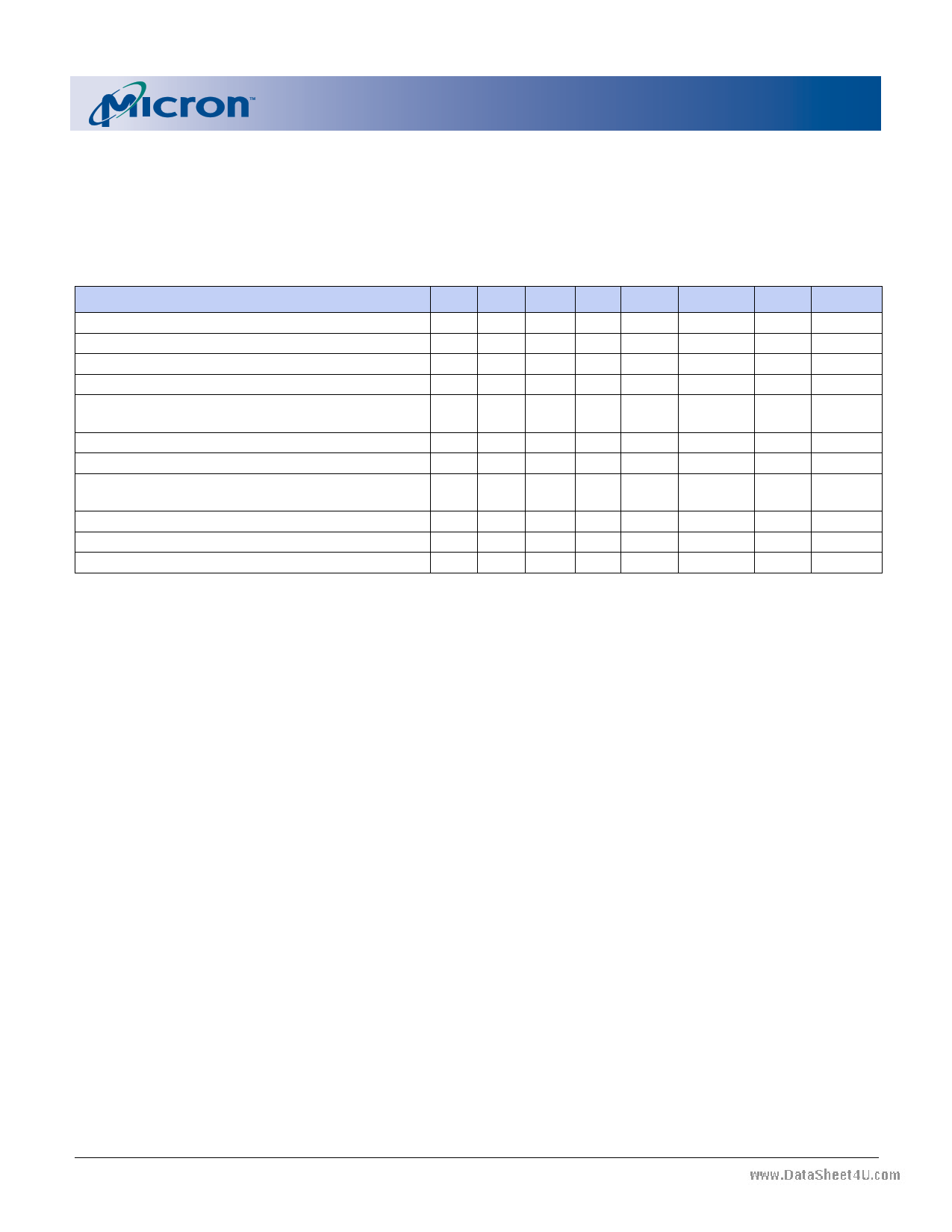

Table 1: Address Table

Refresh Count

Device Banks

Device Configuration

Row Addressing

Column Addressing

Module Banks

256MB

MODULE

8K

4 (BA0, BA1)

32 Meg x 8

8K (A0–A12)

1K (A0–A9)

1 (S0,S2)

512MB

MODULE

8K

4 (BA0, BA1)

32 Meg x 8

8K (A0–A12)

1K (A0–A9)

2 (S0,S2; S1,S3)

Figure 1: 168-Pin DIMM (MO–161)

Standard

Low Profile

Table 2: Timing parameters

MODULE

MARKINGS

-13E

-133

-10E

PC100

CL - tRCD - tRP

2-2-2

2-2-2

2-2-2

PC133

CL - tRCD - tRP

2-2-2

3-3-3

NA

Table 3: Part Numbers

PARTNUMBER1

SYSTEM

CONFIGURATION BUS SPEED

MT8LSDT3264AG-13E_

32 Meg x 64 133 MHz

MT8LSDT3264AG(I)-133_ 32 Meg x 64 133 MHz

MT8LSDT3264AG-10E_

32 Meg x 64 100 MHz

MT16LSDT6464AG-13E_

64 Meg x 64 133 MHz

MT16LSDT6464AG(I)-133_ 64 Meg x 64 133 MHz

MT16LSDT6464AG-10E_

64 Meg x 64 100 MHz

NOTE:

1. The designators for component and PCB revision

are the last two characters of each part number.

Consult factory for current revision codes. Example:

MT8LSDT3264AG-133B1.

32,64 Meg x 64 SDRAM DIMMs

SD8_16C32_64x64AG_C.fm - Rev. C 11/02

1 Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2002, Micron Technology Inc.

1 page

www.DataSheet4U.com

256MB / 512MB (x64)

168-PIN SDRAM DIMMs

Figure 3: Functional Block Diagram

Single Bank Modules

S0#

DQMB0

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

DQMB1

DQ8

DQ9

DQ10

DQ11

DQ12

DQ13

DQ14

DQ15

DQM CS#

DQ

DQ

DQ

DQ U1

DQ

DQ

DQ

DQ

DQM CS#

DQ

DQ

DQ

DQ U3

DQ

DQ

DQ

DQ

DQMB4

DQ32

DQ33

DQ34

DQ35

DQ36

DQ37

DQ38

DQ39

DQMB5

DQ40

DQ41

DQ42

DQ43

DQ44

DQ45

DQ46

DQ47

DQM CS#

DQ

DQ

DQ

DQ U2

DQ

DQ

DQ

DQ

DQM CS#

DQ

DQ

DQ

DQ U4

DQ

DQ

DQ

DQ

S2#

DQMB2

DQ16

DQ17

DQ18

DQ19

DQ20

DQ21

DQ22

DQ23

DQMB3

DQ24

DQ25

DQ26

DQ27

DQ28

DQ29

DQ30

DQ31

DQM CS#

DQ

DQ

DQ

DQ U7

DQ

DQ

DQ

DQ

DQM CS#

DQ

DQ

DQ

DQ U9

DQ

DQ

DQ

DQ

DQMB6

DQ48

DQ49

DQ50

DQ51

DQ52

DQ53

DQ54

DQ55

DQMB7

DQ56

DQ57

DQ58

DQ59

DQ60

DQ61

DQ62

DQ63

DQM CS#

DQ

DQ

DQ

DQ U6

DQ

DQ

DQ

DQ

DQM CS#

DQ

DQ

DQ

DQ U8

DQ

DQ

DQ

DQ

RAS#

CAS#

CKE0

WE#

A0-A11

BA0

BA1

VDD

VSS

RAS#: SDRAMs

CAS#: SDRAMs

CKE0: SDRAMs

WE#: SDRAMs

A0-A11: SDRAMs

BA0: SDRAMs

BA1: SDRAMs

SDRAMs

SDRAMs

SPD

SCL U10

SDA

WP A0 A1 A2

SA0 SA1 SA2

Notes:

All resistor values are 10W unless otherwise specified.

Per industry standard, Micron modules use various component speed grades as

referenced in the module part numbering guide at:

www.micron.com/numberguide.

CK0

CK2

3.3pF

CK1, CK3

U1

U2

U3

U4

U5

U6

U7

U8

U9

10pF

SDRAMs = MT48LC32M8A2TG, Commercial Temperature

SDRAMs = MT48LC32M8A2TG-75 IT, Industrial Temperature

32,64 Meg x 64 SDRAM DIMMs

SD8_16C32_64x64AG_C.fm - Rev. C 11/02

5 Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2002, Micron Technology Inc.

5 Page

www.DataSheet4U.com

256MB / 512MB (x64)

168-PIN SDRAM DIMMs

Commands

The Truth Table provides a quick reference of avail-

able commands. This is followed by written descrip-

tion of each command. For a more detailed descrip-

tion of commands and operations, refer to the 256Mb

SDRAM component data sheet.

Table 9: Truth Table – SDRAM Commands and DQMB Operation

CKE is HIGH for all commands shown except SELF REFRESH; notes appear following the Truth Table

NAME (FUNCTION)

CS# RAS# CAS# WE# DQMB ADDR DQ

COMMAND INHIBIT (NOP)

HX XX

X

X

X

NO OPERATION (NOP)

L H HH

X

X

X

ACTIVE (Select bank and activate row)

L L H H X Bank/Row X

READ (Select bank and column, and start READ burst) L H L H L/H Bank/Col X

WRITE (Select bank and column, and start WRITE

burst)

L H L L L/H Bank/Col Valid

BURST TERMINATE

LHHL

X

X Active

PRECHARGE (Deactivate row in bank or banks)

L L H L X Code X

AUTO REFRESH or SELF REFRESH

(Enter self refresh mode)

LL LH X X X

LOAD MODE REGISTER

LL

LL

X Op-code X

Write Enable/Output Enable

–– ––

L

– Active

Write Inhibit/Output High-Z

–––– H

– High-Z

NOTES

1

2

2

3

4, 5

6

7

7

NOTE:

1. A0–A12 provide row address; BA0–BA1 determine which device bank is made active.

2. A0–A9 provide column address; A10 HIGH enables the auto-precharge feature (nonpersistent), while A10 LOW dis-

ables the auto-precharge feature; BA0-BA1 determine which device bank is being read from or written to.

3. A10 LOW: BA0–BA1 determine which device bank is being precharged. A10 HIGH: all device banks are precharged

and BA0, BA1 are “Don’t Care.”

4. This command is AUTO REFRESH if CKE is HIGH, SELF REFRESH if CKE is LOW.

5. Internal refresh counter controls row addressing; all inputs and I/Os are “Don’t Care” except for CKE.

6. A0–A11 define the op-code written to the mode register and A12 should be driven LOW.

7. Activates or deactivates the DQs during WRITEs (zero-clock delay) and READs (two-clock delay).

32,64 Meg x 64 SDRAM DIMMs

SD8_16C32_64x64AG_C.fm - Rev. C 11/02

11

Micron Technology, Inc., reserves the right to change products or specifications without notice.

©2002, Micron Technology Inc.

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet MT16LSDT6464A.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MT16LSDT6464A | SYNCHRONOUS DRAM MODULE | Micron Technology |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |