|

|

PDF STK14D88 Data sheet ( Hoja de datos )

| Número de pieza | STK14D88 | |

| Descripción | 32Kx8 Autostore nvSRAM | |

| Fabricantes | Simtek | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de STK14D88 (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

STK14D88

32Kx8 Autostore nvSRAM

FEATURES

• 25, 35, 45 ns Read Access & R/W Cycle Time

• Unlimited Read/Write Endurance

• Automatic Non-volatile STORE on Power Loss

• Non-Volatile STORE Under Hardware or Software

Control

• Automatic RECALL to SRAM on Power Up

• Unlimited RECALL Cycles

• 200K STORE Cycles

• 20-Year Non-volatile Data Retention

• Single 3V +20%, -10% Power Supply

• Commercial, Industrial Temperatures

• Small Footprint SOIC & SSOP Packages (RoHS-

Compliant

DESCRIPTION

The Simtek STK14D88 is a 256Kb fast static RAM

with a non-volatile Quantum Trap storage element

included with each memory cell.

The SRAM provides the fast access & cycle times,

ease of use and unlimited read & write endurance of

a normal SRAM.

Data transfers automatically to the non-volatile stor-

age cells when power loss is detected (the STORE

operation). On power up, data is automatically

restored to the SRAM (the RECALL operation). Both

STORE and RECALL operations are also available

under software control.

The Simtek nvSRAM is the first monolithic non-vola-

tile memory to offer unlimited writes and reads. It is

the highest performance, most reliable non-volatile

memory available.

BLOCK DIAGRAM

A5

A6

A7

A8

A9

A11

A12

A13

A14

DQ0

DQ1

DQ2

DQ3

DQ4

DQ5

DQ6

DQ7

Quatum Trap

512 X 512

STATIC RAM

ARRAY

512 X 512

STORE

RECALL

COLUMN I/O

COLUMN DEC

A0 A1 A2 A3 A4 A10

This product conforms to specifications per the

terms of Simtek standard warranty. The product

has completed Simtek internal qualification testing

and has reached production status.

1

VCC VCAP

POWER

CONTROL

STORE/

RECALL

CONTROL

HSB

SOFTWARE

DETECT

A13 – A0

G

E

W

Document Control #ML0033 Rev 1.7

February 2007

1 page

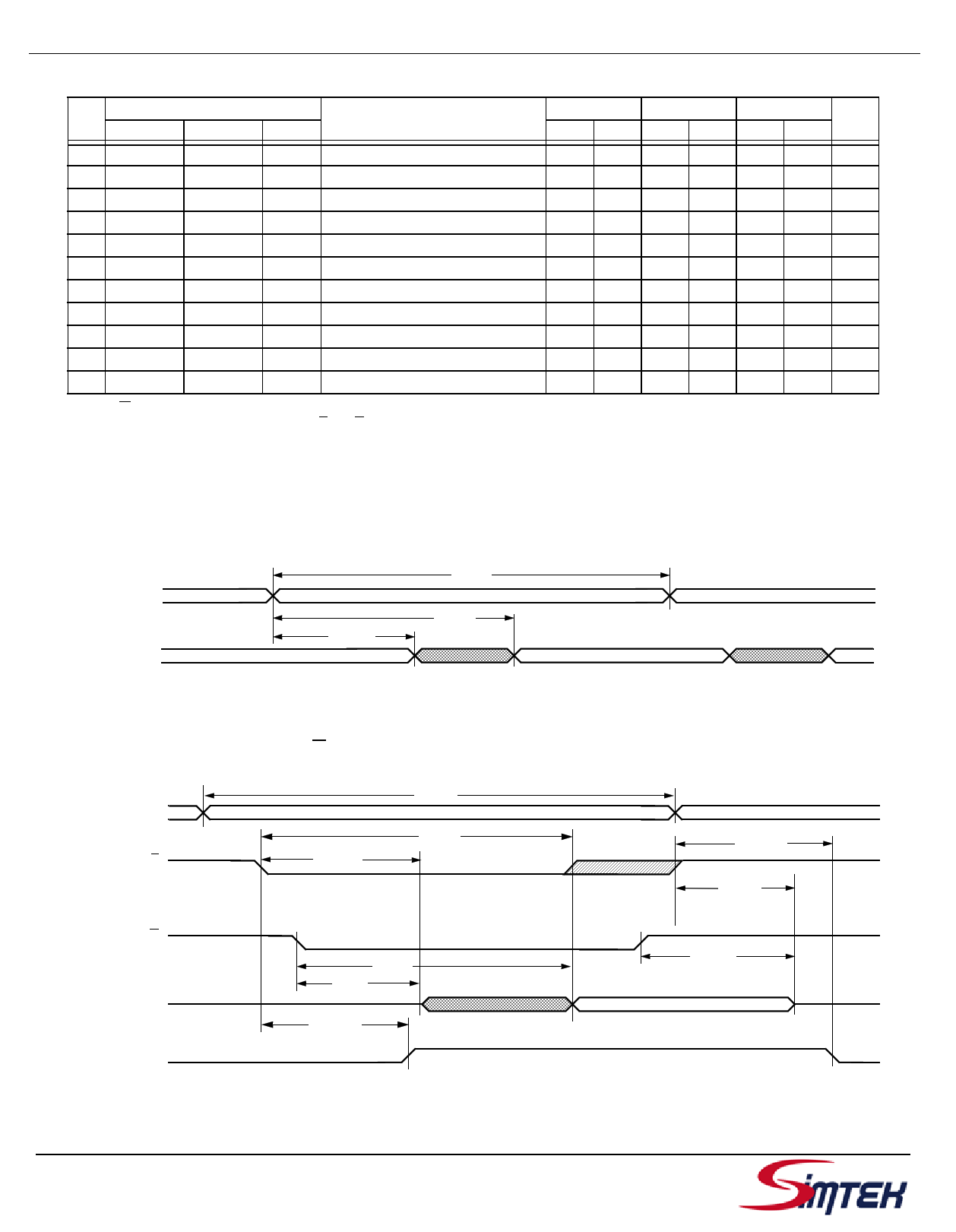

SRAM READ CYCLES #1 & #2

SYMBOLS

NO.

#1 #2 Alt.

PARAMETER

1

2 tAVAVc

3 tAVQVd

4

5 tAXQXd

6

7

8

9

10

11

tELQV

tAVAVc

tAVQVd

tGLQV

tAXQXd

tELQX

tEHQZe

tGLQX

tGHQZe

tELICCHb

tEHICCLb

tACS

tRC

tAA

tOE

tOH

tLZ

tHZ

tOLZ

tOHZ

tPA

tPS

Chip Enable Access Time

Read Cycle Time

Address Access Time

Output Enable to Data Valid

Output Hold after Address Change

Chip Enable to Output Active

Chip Disable to Output Inactive

Output Enable to Output Active

Output Disable to Output Inactive

Chip Enable to Power Active

Chip Disable to Power Standby

Note c:

Note d:

Note e:

Note f:

W must be high during SRAM READ cycles.

Device is continuously selected with E and G both low

Measured ± 200mV from steady state output voltage.

HSB must remain high during READ and WRITE cycles.

STK14D88

STK14D88-25

MIN MAX

25

25

25

12

3

3

10

0

10

0

25

STK14D88-35

MIN MAX

35

35

35

15

3

3

13

0

13

0

35

STK14D88-45

MIN MAX

45

45

45

20

3

3

15

0

15

0

45

UNITS

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

SRAM READ CYCLE #1: Address Controlledc,d,f

ADDRESS

DQ (DATA OUT)

5

tAXQX

2

tAVAV

3

tAVQV

DATA VALID

SRAM READ CYCLE #2: E Controlledc,f

ADDRESS

E

6

tELQX

2

tAVAV

1

tELQV

G

DQ (DATA OUT)

ICC

8

tGLQX

4

tGLQV

10

tELICCH

STANDBY

ACTIVE

11

tEHICCL

7

tEHQZ

9

tGHQZ

DATA VALID

Document Control #ML0033 Rev 1.7

February 2007

5

5 Page

nvSRAM OPERATION

STK14D88

nvSRAM

The STK14D88 nvSRAM is made up of two func-

tional components paired in the same physical cell.

These are the SRAM memory cell and a nonvolatile

QuantumTrap cell. The SRAM memory cell operates

like a standard fast static RAM. Data in the SRAM

can be transferred to the nonvolatile cell (the

STORE operation), or from the nonvolatile cell to

SRAM (the RECALL operation). This unique archi-

tecture allows all cells to be stored and recalled in

parallel. During the STORE and RECALL operations

SRAM READ and WRITE operations are inhibited.

The STK14D88 supports unlimited read and writes

like a typical SRAM. In addition, it provides unlimited

RECALL operations from the nonvolatile cells and

up to 200K STORE operations.

SRAM READ

The STK14D88 performs a READ cycle whenever E

and G are low while W and HSB are high. The

address specified on pins A0-16 determine which of

the 32,768 data bytes will be accessed. When the

READ is initiated by an address transition, the out-

puts will be valid after a delay of tAVQV (READ cycle

#1). If the READ is initiated by E and G, the outputs

will be valid at tELQV or at tGLQV, whichever is later

(READ cycle #2). The data outputs will repeatedly

respond to address changes within the tAVQV

access time without the need for transitions on any

control input pins, and will remain valid until another

address change or until E or G is brought high, or W

and HSB is brought low.

VCAP

VCC

VCC

W

Figure 3: AutoStore Mode

SRAM WRITE

A WRITE cycle is performed whenever E and W are

low and HSB is high. The address inputs must be

stable prior to entering the WRITE cycle and must

remain stable until either E or W goes high at the

end of the cycle. The data on the common I/O pins

DQ0-7 will be written into memory if it is valid tDVWH

before the end of a W controlled WRITE or tDVEH

before the end of an E controlled WRITE.

It is recommended that G be kept high during the

entire WRITE cycle to avoid data bus contention on

common I/O lines. If G is left low, internal circuitry

will turn off the output buffers tWLQZ after W goes

low.

AutoStore OPERATION

The STK14D88 stores data to nvSRAM using one of

three storage operations. These three operations

are Hardware Store (activated by HSB), Software

Store (activated by an address sequence), and

AutoStore (on power down).

AutoStore operation is a unique feature of Simtek

QuanumTrap technology is enabled by default on

the STK14D88.

During normal operation, the device will draw cur-

rent from VCC to charge a capacitor connected to

the VCAP pin. This stored charge will be used by the

chip to perform a single STORE operation. If the

voltage on the VCC pin drops below VSWITCH, the

part will automatically disconnect the VCAP pin from

VCC. A STORE operation will be initiated with power

provided by the VCAP capacitor.

Figure 3 shows the proper connection of the storage

capacitor (VCAP) for automatic store operation.

Refer to the DC CHARACTERISTICS table for the

size of VCAP. The voltage on the VCAP pin is driven

to 5V by a charge pump internal to the chip. A pull

up should be placed on W to hold it inactive during

power up.

To reduce unneeded nonvolatile stores, AutoStore

and Hardware Store operations will be ignored

unless at least one WRITE operation has taken

place since the most recent STORE or RECALL

cycle. Software initiated STORE cycles are per-

formed regardless of whether a WRITE operation

Document Control #ML0033 Rev 1.7

February 2007

11

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet STK14D88.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| STK14D88 | 32Kx8 Autostore nvSRAM | Simtek |

| STK14D88-3 | 32K x 8 SRAM / CMOS | Simtek |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |