|

|

PDF LM2748 Data sheet ( Hoja de datos )

| Número de pieza | LM2748 | |

| Descripción | (LM2745 / LM2748) Synchronous Buck Controller | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de LM2748 (archivo pdf) en la parte inferior de esta página. Total 23 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

May 2005

LM2745/8

Synchronous Buck Controller with Pre-bias Startup, and

Optional Clock Synchronization

General Description

The LM2745/8 are high-speed synchronous buck regulator

controllers with an accurate feedback voltage accuracy of

±1.5%. It can provide simple down conversion to output

voltages as low as 0.6V. Though the control sections of the

IC are rated for 3 to 6V, the driver sections are designed to

accept input supply rails as high as 14V. The use of adaptive

non-overlapping MOSFET gate drivers helps avoid potential

shoot-through problems while maintaining high efficiency.

The IC is designed for the more cost-effective option of

driving only N-channel MOSFETs in both the high-side and

low-side positions. It senses the low-side switch voltage drop

for providing a simple, adjustable current limit.

The LM2745/8 features a fixed-frequency voltage-mode

PWM control architecture which is adjustable from 50 kHz to

1 MHz with one external resistor. In addition, the LM2745

also allows the switching frequency to be synchronized to an

external clock signal over the range of 250 kHz to 1 MHz.

This wide range of switching frequency gives the power

supply designer the flexibility to make better tradeoffs be-

tween component size, cost and efficiency.

Features include the ability to startup with a pre-biased load

on the output, soft-start, input undervoltage lockout (UVLO)

and Power Good (based on both undervoltage and overvolt-

age detection). In addition, the shutdown pin of the IC can be

used for providing startup delay, and the soft-start pin can be

used for implementing precise tracking, for the purpose of

sequencing with respect to an external rail.

Features

n Switching frequency from 50 kHz to 1 MHz

n Switching frequency synchronize range 250 kHz to 1

MHz (LM2745 Only)

n Startup with a pre-biased output load

n Power stage input voltage from 1V to 14V

n Control stage input voltage from 3V to 6V

n Output voltage adjustable down to 0.6V

n Power Good flag and shutdown

n Output overvoltage and undervoltage detection

n ±1.5% feedback voltage accuracy over temperature

n Low-side adjustable current sensing

n Adjustable soft-start

n Tracking and sequencing with shutdown and soft start

pins

n TSSOP-14 package

Applications

n Down Conversion from 3.3V

n Cable Modem, DSL and ADSL

n Laser Jet and Ink Jet Printers

n Low Voltage Power Modules

n DSP, ASIC, Core and I/O

Typical Application

© 2005 National Semiconductor Corporation DS201374

20137401

www.national.com

1 page

Typical Performance Characteristics

Efficiency (VOUT = 1.2V)

VCC = 3.3V, fSW = 1 MHz

Internal Reference Voltage vs Temperature

20137440

Frequency vs Temperature

20137458

Output Voltage vs Output Current

20137460

Switch Waveforms

VCC = 3.3V, VIN = 5V, VOUT = 1.2V

IOUT = 3A, CSS = 12 nF, fSW = 1 MHz

20137456

Start-Up (Full-Load)

VCC = 3.3V, VIN = 5V, VOUT = 1.2V

IOUT = 3A, CSS = 12 nF, fSW = 1 MHz

20137446

5

20137448

www.national.com

5 Page

Application Information (Continued)

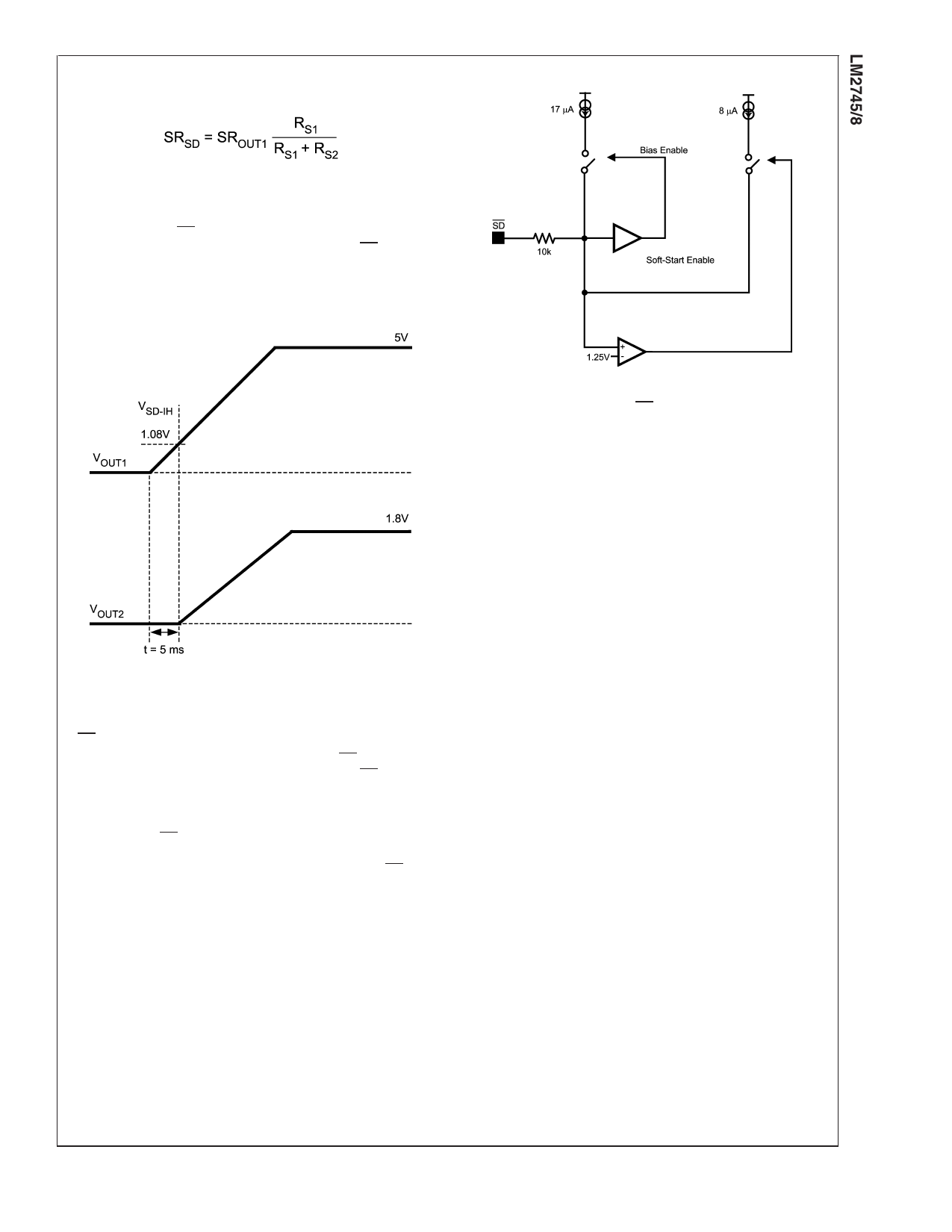

For example, if the master supply output voltage slew rate

was 1V/ms and the desired delay time between the startup

of the master supply and LM2745/8 output voltage was 5 ms,

then the desired SD pin slew rate would be (1.08V/5 ms) =

0.216V/ms. Due to the internal impedance of the SD pin, the

maximum recommended value for RS2 is 1 kΩ. To achieve

the desired slew rate, RS1 would then be 274Ω. A timing

diagram for this example is shown in Figure 7.

FIGURE 7. Delay for Sequencing

20137411

SD PIN IMPEDANCE

When connecting a resistor divider to the SD pin of the

LM2745/8 some care has to be taken. Once the SD voltage

goes above VSD-IH, a 17 µA pull-up current is activated as

shown in Figure 8. This current is used to create the internal

hysteresis ()170 mV); however, high external impedances

will affect the SD pin logic thresholds as well. The external

impedance used for the sequencing divider network should

preferably be a small fraction of the impedance of the SD pin

for good performance (around 1 kΩ).

FIGURE 8. SD Pin Logic

20137406

MOSFET GATE DRIVERS

The LM2745/8 has two gate drivers designed for driving

N-channel MOSFETs in a synchronous mode. Note that

unlike most other synchronous controllers, the bootstrap

capacitor of the LM2745/8 provides power not only to the

driver of the upper MOSFET, but the lower MOSFET driver

too (both drivers are ground referenced, i.e. no floating

driver).

Two things must be kept in mind here. First, the BOOT pin

has an absolute maximum rating of 18V. This must never be

exceeded, even momentarily. Since the bootstrap capacitor

is connected to the SW node, the peak voltage impressed on

the BOOT pin is the sum of the input voltage (VIN) plus the

voltage across the bootstrap capacitor (ignoring any forward

drop across the bootstrap diode). The bootstrap capacitor is

charged up by a given rail (called VBOOT_DC here) whenever

the upper MOSFET turns off. This rail can be the same as

VCC or it can be any external ground-referenced DC rail. But

care has to be exercised when choosing this bootstrap DC

rail that the BOOT pin is not damaged. For example, if the

desired maximum VIN is 14V, and VBOOT_DC is chosen to be

the same as VCC, then clearly if the VCC rail is 6V, the peak

voltage on the BOOT pin is 14V + 6V = 20V. This is unac-

ceptable, as it is in excess of the rating of the BOOT pin. A

VCC of 3V would be acceptable in this case. Or the VIN range

must be reduced accordingly. There is also the option of

deriving the bootstrap DC rail from another 3V external rail,

independent of VCC.

The second thing to be kept in mind here is that the output of

the low-side driver swings between the bootstrap DC rail

level of VBOOT_DC and Ground, whereas the output of the

high-side driver swings between VIN+ VBOOT_DC and

Ground. To keep the high-side MOSFET fully on when de-

sired, the Gate pin voltage of the MOSFET must be higher

than its instantaneous Source pin voltage by an amount

equal to the ’Miller plateau’. It can be shown that this plateau

is equal to the threshold voltage of the chosen MOSFET plus

a small amount equal to Io/g. Here Io is the maximum load

current of the application, and g is the transconductance of

this MOSFET (typically about 100 for logic-level devices).

That means we must choose VBOOT_DC to at least exceed

11 www.national.com

11 Page | ||

| Páginas | Total 23 Páginas | |

| PDF Descargar | [ Datasheet LM2748.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| LM27402 | LM27402 High-Performance Synchronous Buck Controller With DCR Current Sensing (Rev. J) | Texas Instruments |

| LM27403 | LM27403 Synchronous Buck Controller With Temperature-Compensated Inductor-DCR-Based Overcurrent Protection and Programmable Thermal Shutdown (Rev. B) | Texas Instruments |

| LM2742 | N-Channel FET Synchronous Buck Regulator Controller for Low Output Voltages | National Semiconductor |

| LM2742 | LM2742 N-Chan FET Synch Buck Reg Cntrlr for Low Output Voltages (Rev. C) | Texas Instruments |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |