|

|

PDF A1020B Data sheet ( Hoja de datos )

| Número de pieza | A1020B | |

| Descripción | (A1010B / A1020B) FPGAs | |

| Fabricantes | Actel Corporation | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de A1020B (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

www.DataSheet4U.com

ACT™ 1 Series FPGAs

Features

• 5V and 3.3V Families fully compatible with JEDEC

specifications

• Up to 2000 Gate Array Gates (6000 PLD equivalent gates)

• Replaces up to 50 TTL Packages

• Replaces up to twenty 20-Pin PAL® Packages

• Design Library with over 250 Macro Functions

• Gate Array Architecture Allows Completely Automatic

Place and Route

• Up to 547 Programmable Logic Modules

• Up to 273 Flip-Flops

• Data Rates to 75 MHz

• Two In-Circuit Diagnostic Probe Pins Support Speed

Analysis to 25 MHz

• Built-In High Speed Clock Distribution Network

• I/O Drive to 10 mA (5 V), 6 mA (3.3 V)

• Nonvolatile, User Programmable

• Fabricated in 1.0 micron CMOS technology

Description

The ACT™ 1 Series of field programmable gate arrays

(FPGAs) offers a variety of package, speed, and application

combinations. Devices are implemented in silicon gate,

1-micron two-level metal CMOS, and they employ Actel’s

PLICE® antifuse technology. The unique architecture offers

gate array flexibility, high performance, and instant

turnaround through user programming. Device utilization is

typically 95 to 100 percent of available logic modules.

ACT 1 devices also provide system designers with unique

on-chip diagnostic probe capabilities, allowing convenient

testing and debugging. Additional features include an on-chip

mclock driver with a hardwired distribution network. The

.conetwork provides efficient clock distribution with minimum

skew.

t4UThe user-definable I/Os are capable of driving at both TTL

eand CMOS drive levels. Available packages include plastic

eand ceramic J-leaded chip carriers, ceramic and plastic quad

hflatpacks, and ceramic pin grid array.

w.DataSApril 1996

ww © 1996 Actel Corporation

A security fuse may be programmed to disable all further

programming and to protect the design from being copied or

reverse engineered.

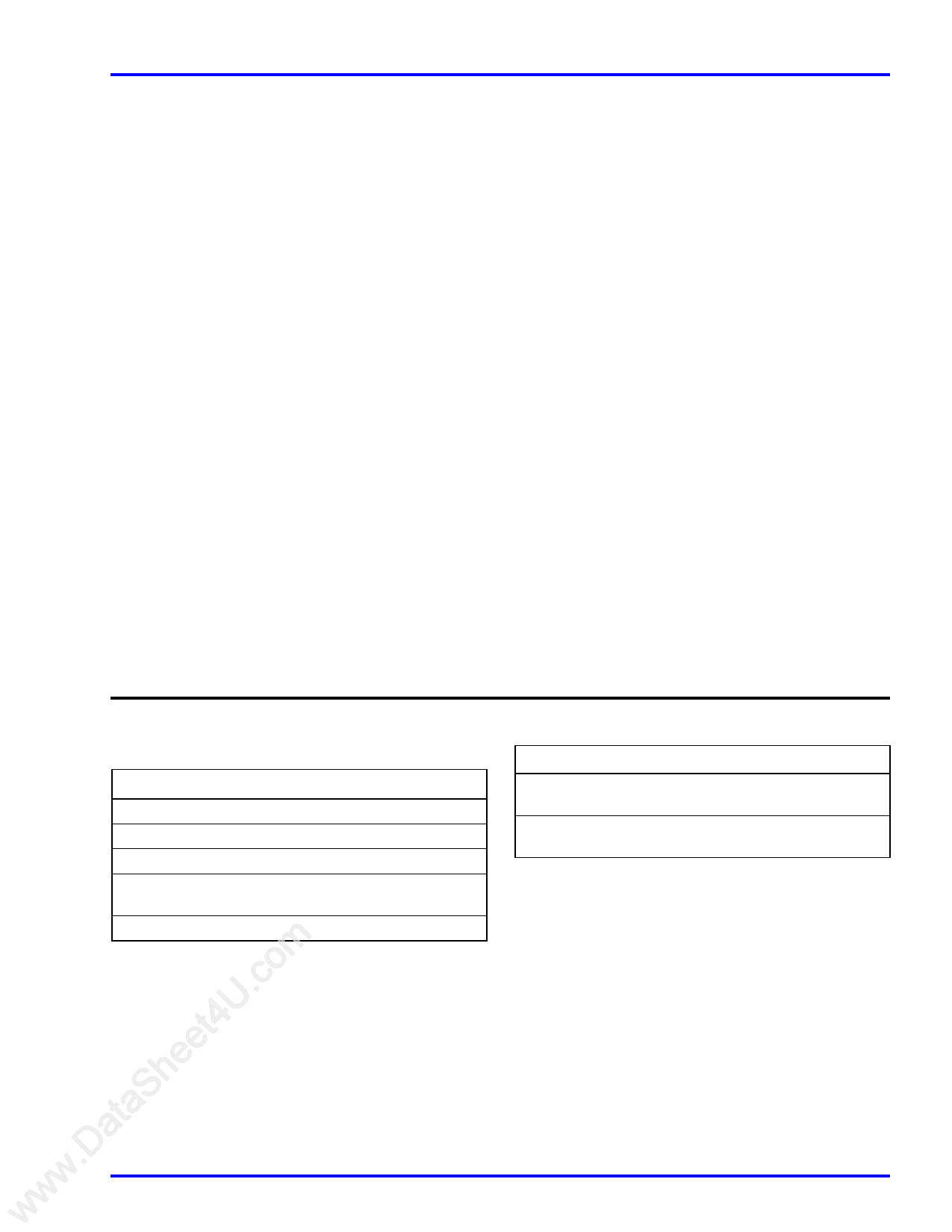

Product Family Profile

Device

A1010B A1020B

A10V10B A10V20B

Capacity

Gate Array Equivalent Gates

PLD Equivalent Gates

TTL Equivalent Packages

20-Pin PAL Equivalent Packages

1,200

3,000

30

12

2,000

6,000

50

20

Logic Modules

295 547

Flip-Flops (maximum)

147 273

Routing Resources

Horizontal Tracks/Channel

Vertical Tracks/Column

PLICE Antifuse Elements

22

13

112,000

22

13

186,000

User I/Os (maximum)

57 69

Packages:

44 PLCC 44 PLCC

68 PLCC 68 PLCC

84 PLCC

100 PQFP 100 PQFP

80 VQFP 80 VQFP

84 CPGA 84 CPGA

84 CQFP

Performance

5 V Data Rate (maximum)

3.3 V Data Rate (maximum)

75 MHz

55 MHz

75 MHz

55 MHz

Note: See Product Plan on page 1-286 for package availability.

The Designer and Designer

Advantage™ Systems

The ACT 1 device family is supported by Actel’s Designer and

Designer Advantage Systems, allowing logic design

implementation with minimum effort. The systems offer

Microsoft® Windows™ and X Windows™ graphical user

interfaces and integrate with the resident CAE system to

provide a complete gate array design environment: schematic

capture, simulation, fully automatic place and route, timing

verification, and device programming. The systems also

include the ACTmap™ VHDL optimization and synthesis tool

and the ACTgen™ Macro Builder, a powerful macro function

generator for counters, adders, and other structural blocks.

1-283

1 page

www.DataSheet4U.com

ACT™ 1 Series FPGAs

Pin Description

CLK

Clock (Input)

TTL Clock input for global clock distribution network. The

Clock input is buffered prior to clocking the logic modules.

This pin can also be used as an I/O.

DCLK

Diagnostic Clock (Input)

TTL Clock input for diagnostic probe and device

programming. DCLK is active when the MODE pin is HIGH.

This pin functions as an I/O when the MODE pin is LOW.

GND

Ground

Input LOW supply voltage.

I/O Input/Output (Input, Output)

I/O pin functions as an input, output, three-state, or

bidirectional buffer. Input and output levels are compatible

with standard TTL and CMOS specifications. Unused I/O pins

are automatically driven LOW by the ALS software.

MODE

Mode (Input)

The MODE pin controls the use of multifunction pins (DCLK,

PRA, PRB, SDI). When the MODE pin is HIGH, the special

functions are active. When the MODE pin is LOW, the pins

function as I/O. To provide Actionprobe capability, the MODE

pin should be terminated to GND through a 10K resistor so

that the MODE pin can be pulled high when required.

NC No Connection

This pin is not connected to circuitry within the device.

PRA

Probe A (Output)

The Probe A pin is used to output data from any user-defined

design node within the device. This independent diagnostic

pin is used in conjunction with the Probe B pin to allow

real-time diagnostic output of any signal path within the

device. The Probe A pin can be used as a user-defined I/O

when debugging has been completed. The pin’s probe

capabilities can be permanently disabled to protect the

programmed design’s confidentiality. PRA is active when the

MODE pin is HIGH. This pin functions as an I/O when the

MODE pin is LOW.

PRB

Probe B (Output)

The Probe B pin is used to output data from any user-defined

design node within the device. This independent diagnostic

pin is used in conjunction with the Probe A pin to allow

real-time diagnostic output of any signal path within the

device. The Probe B pin can be used as a user-defined I/O

when debugging has been completed. The pin’s probe

capabilities can be permanently disabled to protect the

programmed design’s confidentiality. PRB is active when the

MODE pin is HIGH. This pin functions as an I/O when the

MODE pin is LOW.

SDI

Serial Data Input (Input)

Serial data input for diagnostic probe and device

programming. SDI is active when the MODE pin is HIGH. This

pin functions as an I/O when the MODE pin is LOW.

VCC

Supply Voltage

Input HIGH supply voltage.

Absolute Maximum Ratings1

Free air temperature range

Symbol Parameter

Limits

Units

VCC

DC Supply Voltage2

–0.5 to +7.0

Volts

VI Input Voltage

–0.5 to VCC +0.5 Volts

VO Output Voltage

–0.5 to VCC +0.5 Volts

IIO I/O Sink/Source

Current3

±20 mA

TSTG Storage Temperature –65 to +150

°C

mNotes:

o1. Stresses beyond those listed under “Absolute Maximum Ratings”

.cmay cause permanent damage to the device. Exposure to

absolute maximum rated conditions for extended periods may

Uaffect device reliability. Device should not be operated outside

t4the Recommended Operating Conditions.

e2. VPP = VCC , except during device programming.

e3. Device inputs are normally high impedance and draw

hextremely low current. However, when input voltage is greater

Sthan VCC + 0.5 V or less than GND – 0.5 V, the internal protection

www.Datadiode will be forward biased and can draw excessive current.

Recommended Operating Conditions

Parameter

Commercial Industrial Military Units

Temperature

Range1

0 to

+70

–40 to

+85

–55 to

+125

°C

Power Supply

Tolerance

±5

±10 ±10 %VCC

Note:

1. Ambient temperature (TA) used for commercial and industrial;

case temperature (TC) used for military.

1-287

5 Page

www.DataSheet4U.com

ACT™ 1 Series FPGAs

Timing Derating

A best case timing derating factor of 0.45 is used to reflect

best case processing. Note that this factor is relative to the

“standard speed” timing parameters, and must be multiplied

by the appropriate voltage and temperature derating factors

for a given application.

Timing Derating Factor (Temperature and Voltage)

Industrial

Military

Min.

Max.

Min.

Max.

(Commercial Minimum/Maximum Specification) x

0.69

1.11

0.67 1.23

Timing Derating Factor for Designs at Typical Temperature (TJ = 25°C) and

Voltage (5.0 V)

(Commercial Maximum Specification) x

0.85

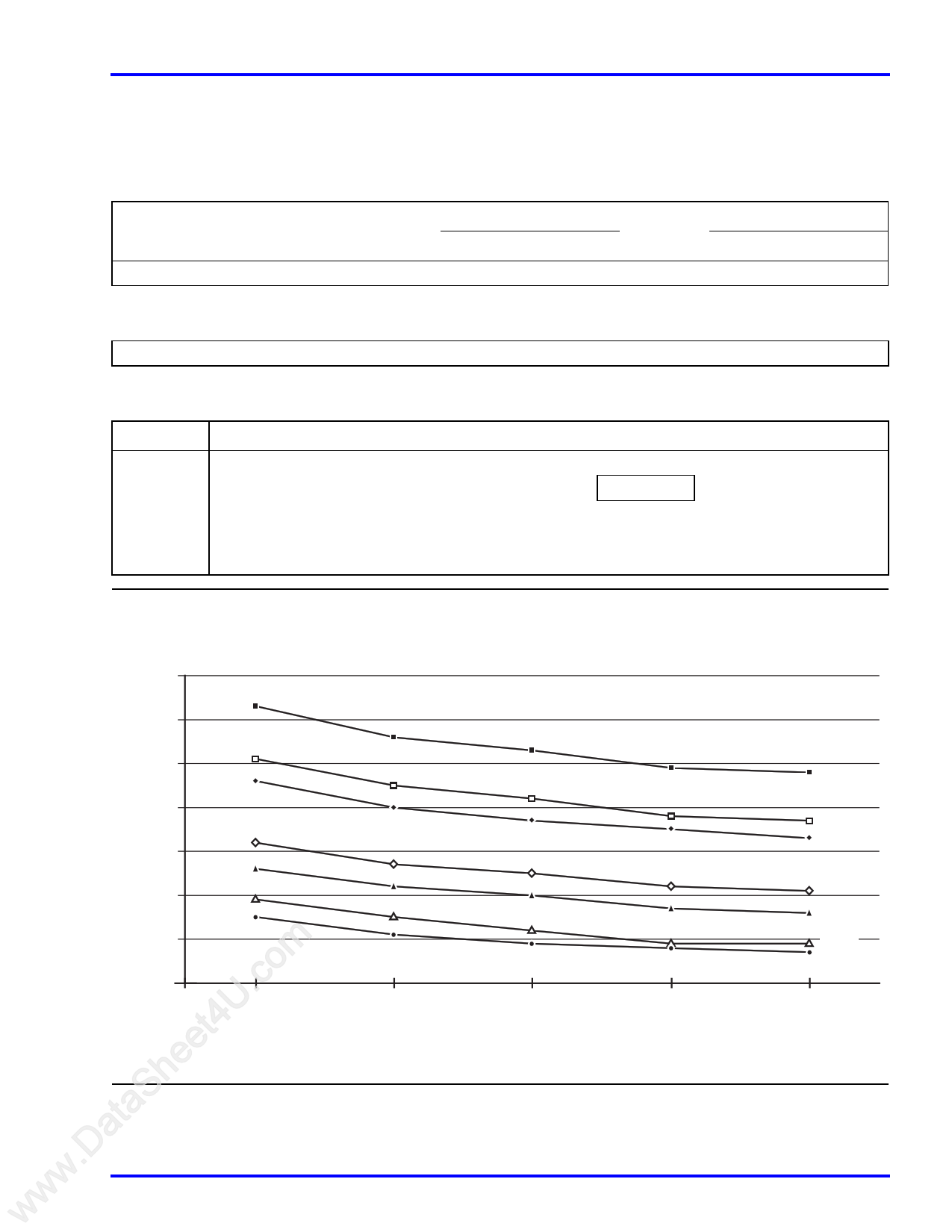

Temperature and Voltage Derating Factors

(normalized to Worst-Case Commercial, TJ = 4.75 V, 70°C)

–55 –40

0

25 70

4.50 0.75 0.79 0.86 0.92 1.06

4.75 0.71 0.75 0.82 0.87 1.00

5.00 0.69 0.72 0.80 0.85 0.97

5.25 0.68 0.69 0.77 0.82 0.95

5.50 0.67 0.69 0.76 0.81 0.93

85

1.11

1.05

1.02

0.98

0.97

125

1.23

1.16

1.13

1.09

1.08

Junction Temperature and Voltage Derating Curves

(normalized to Worst-Case Commercial, TJ = 4.75 V, 70°C)

1.3

1.2

1.1

1.0

0.9

0.8

0.7

.com0.6

t4U4.50

4.75 5.00

Voltage (V)

www.DataSheeNote: This derating factor applies to all routing and propagation delays.

5.25

125°C

85°C

70°C

25°C

0°C

–40°C

–55°C

5.50

1-293

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet A1020B.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| A1020 | Silicon PNP Epitaxial Transistor | ETC |

| A1020 | PNP Transistor - 2SA1020 | Toshiba Semiconductor |

| A1020B | (A1010B / A1020B) FPGAs | Actel Corporation |

| A1020B | FPGAs | Actel |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |