|

|

PDF TP3094V Data sheet ( Hoja de datos )

| Número de pieza | TP3094V | |

| Descripción | Quad PCM Codec/Filter | |

| Fabricantes | National Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de TP3094V (archivo pdf) en la parte inferior de esta página. Total 19 Páginas | ||

|

No Preview Available !

February 2000

TP3094 COMBO®

Quad PCM Codec/Filter

General Description

The TP3094 is a monolithic PCM Codec and Fil-

ter device implemented using a digital signal pro-

cessing architecture. It provides four voice

channels, combining transmit bandpass and re-

ceive low pass channel filters with companding A-

law or m-law PCM encoders and decoders. The

device is fabricated using National’s advanced

CMOS process.

The device includes anti-aliasing filters and sig-

ma-delta converters dedicated to each channel,

and by a common signal processing unit which

performs all the remaining filtering and process-

ing for the four channels.

The TP3094 includes a flexible PCM digital inter-

face, which allows the device to be connected to

PCM busses of different formats. It can also be

connected with other TP3094 devices in a cas-

cade fashion, for a system with up to 128 POTS

interfaces (when a 2.048MHz PCM bus is used).

Connection Diagram

Features

• Handles four voice channels

• Complete Codec and Filter system including:

- Transmit and receive channel filters

- A-law or µ-law companding encoder/decoder

• Power down mode for low power consumption

• Compatible to standard time division multi-

plexed PCM bus

- 8 bit mode, frame signal from external reference

- 32 bit mode, internal TSA, with consecutive TS

• Up to 128 channels (32 devices) can be cas-

caded

• Programmable functions (common for all 4

channels):

- A-law or µ-law

- Single MCLK clock,automatically selectable from

8.192MHz, 4.096MHz, 2.048MHz and

1.536/1.544MHz

- Digital and Analog loopback test modes

• Designed for CCITT and LSSGR applications

• Single +5V power supply

• 44 lead PLCC surface mount package

• Maximize line card circuit density

• Use in Central Office, Loop Carrier, and PBX

equipment subscriber line and trunk cards

• Wide operating temperature range -40°C to

85°C

AGND1

VXI2

GXO2

VRO2

NC

VRO1

GXO1

VXI1

NF

AGND0

VXI0

6 5 4 3 2 1 44 43 42 41 40

7 39

8 38

9 37

10 36

11

12 TP3094

35

34

13 33

14 32

15 31

16 30

17 29

18 19 20 21 22 23 24 25 26 27 28

DX

DGND

PT4

DVCC

FSX3

NC

FSR3

FSX2

FSR2

FSX1

FSR1

Order Number TP3094V

See NS Package V44A

COMBO® and TRI-STATE® are registered trademarks of National Semiconductor Corporation

© 2000 National Semiconductor Corporation

www.national.com

1 page

When both the transmit and receive frame sync of

a channel are missing the channel will go into

Power Down Mode (if only one of them is missing

the channel will not go into Power Down). A max-

imum of 32 frame sync pulses must be missing

for power down and the channel will achieve its

reset state after 32.5us. The channel will recover

from power down, within the time of 4ms after the

frame syncs (transmit or receive) will be active.

When the device is in 32-bit mode, missing FSX0,

FSR0 for 512us, will force all channels in power

down mode.

When the master clock MCLK is missing, all the

channels will go into the Global Power Down

Mode, with the lowest possible power consump-

tion. The device will recover from this mode,

when the clock signal comes back (and at least

one frame sync is present), and then the active

channels will operate after less than 100ms.

The device will go into the same Global Power

Down Mode when all the frame syncs (of all the

channels, in case of 8bit mode, the FSX0, FSR0

in case of 32-bit mode) are not present or when

all 4 PDN signals are active. The recovery time

from this mode for the first active channel is less

than 100ms.

Transmit Section

The transmit section input is an operational ampli-

fier, with provision for gain adjustment using two

external resistors. Only the inverting input is pro-

vided (together with the output), this allows, be-

side the adjustment of the gain, to implement the

echo balance function with external passive com-

ponents.

The opamp drives the antialiasing input filter, fol-

lowed by the A to D converter, which provides the

digital input to the signal processing unit.

The signal processing unit accepts the signal

samples from each channel input stage, performs

the necessary decimation and filtering function,

PCM compression and provides the eight bit

samples to the PCM interface block.

The analog input is dc biased at the value of 2.4V.

A DC decoupling is necessary between this input

and the SLIC output. The maximum analog signal

level, at the op-amp output, is 1.12Vrms.

Maximum recommended transmit gain is 20dB

(10x).

Receive Section

This section takes the 8 bit samples from the

PCM interface block and performs all the signal

processing functions, such as PCM expansion

according to the ALaw or uLaw and signal filter-

ing. Then, for each channel it drives the Digital to

Analog converter, through the proper interpola-

tion stages and filters. Finally the signal is filtered

and buffered to the output receive pin. The maxi-

mum output level voltage on the VRO pins on a

load of 5kOhm+100pF is 1.12Vrms.

PCM Interface

The PCM interface consists of the following sig-

nals

• DX, DR - transmit and receive digital signals,

carrying the pcm samples

• FSX0-3, FSR0-3 - transmit and receive frame

signals

• TSX - output time slots signal, indicating the

time slot occupied on the DX by the device

• PCMMode - PCM interface select

PCMMode = HIGH PCMMode = LOW

32 bit

8 bit

• A/uLaw - A-law/ u-law select signal

•

TABLE 1. A/uLaw Coding

A/uLaw = HIGH A/uLaw = LOW

A-law

u-law

• MCLK - bit clock signal

MCLK is both the system master clock and the

PCM bus bit clock, and it is selected internally to

be either 8.192MHz, 4.096MHz, 2.048MHz, or

1.536/ 1.544MHz.

The internal clock selection is perfomed, based

on the relative ratio between the frame signals

(FS) and the clock signals. For proper functional-

ity all the channel FS must have the same valid

rate of 8kHz (giving a valid clock rate). In case

one of the frame syncs runs other than 8kHz, the

device will not function properly.

Each bit on DX is clocked out on the rising edges

of the bit clock (MCLK), starting from the Most

Significant Bit (Sign bit). Each bit on DR is

clocked in on the falling edges of the bit clock,

starting from the MSB.

The device may operate on to the PCM bus in two

modes, selected by the input pin PCMMode;

when PCMMode is “0V” the 8bit mode is selected

and when PCMMode is “+5V” the 32-bit mode is

selected.

5 www.national.com

5 Page

Absolute Maximum Ratings

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Dis-

tributors for availability and specifications.

VCC to DGND

Voltage at any digital inputs or outputs

Voltage at any analog inputs or outputs

Storage temperature range

Lead temperature(Soldering, 10 Sec)

7V

VCC +0.3V to DGND -0.3V

VCC +0.3V to AGND-0.3V

-65oC to +150oC

260oC

ESD (human body model)

2000 V

Latch-up immunity on any pin

200 mA

Electrical Characteristics

Unless otherwise noted, limits printed in bold characters are guaranteed for VCC(all supplies)=5.0V±5%,

DGND=AGND=0V, TA=-40°C to 85°C by correlation with 100% electrical testing at TA=25°C. All other limits are

assured by correlation with other production tests and/or product design and characterization. All digital signals

are referenced to DGND, and all analog signals are referenced to AGND. Typical are specified at VCC=+5V,

TA=25°C.

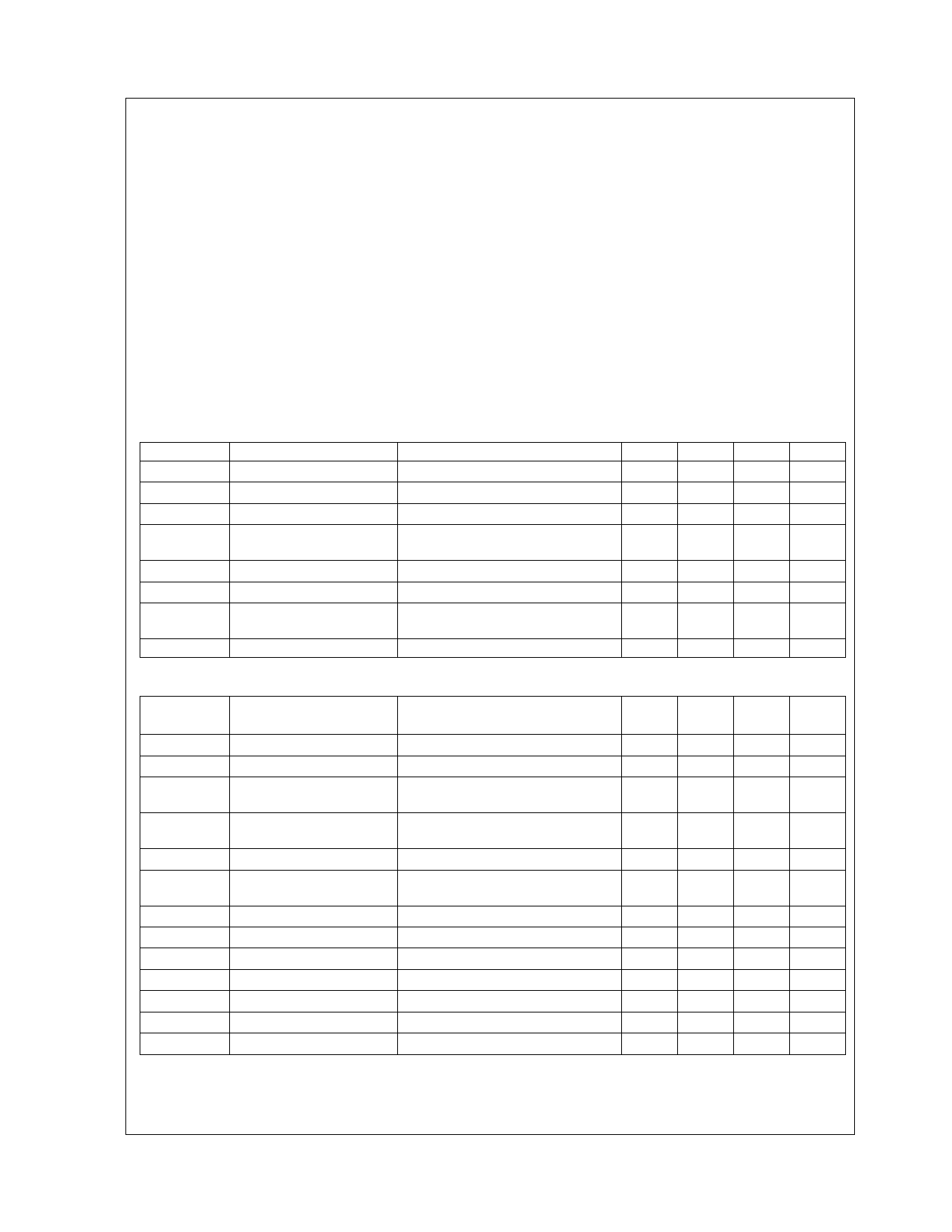

Digital Interface

Symbol

Parameter

Conditions

Min Typ Max Units

VIL

Input low voltage

All digital inputs

0.8 V

VIH

Input high voltage

All digital inputs

VOL

Output low voltage

IL=2mA

VOH

Output high voltage

IL=-2mA

IL=-100uA

2.2 V

0.4 V

2.4 V

3.5 V

IIL

Input low current

DGND<VIN<VIL, all digital inputs -10

IIH

Input high current

VIH<VIN<VCC, all digital inputs

-10

IOZ

Output current in high

DGND<VO<VCC (DX)

impedance state

-10

10 µA

10 µA

10 µA

Ci Input Capacitance

10 pF

Analog Interface

IXI Input leakage current

RXI

CXI

VCMXI

VCMXO

RRO

RROZ

RLRO

CLRO

AVXA

FUXA

RLGXO

CLGXO

VRO

Input resistance

Input capacitance

Transmit input common

mode voltage range

Receive input common

mode voltage range

Output resistance

Output resistance in

PDN

Load resistance

Load capacitance

Voltage Gain

Unity Gain Bandwidth

Load resistance

Load capacitance

RX output drive level

1V<VXI<4V, all analog inputs in

Power UP mode

1V<VXI<4V, all analog inputs

1V<VXI<4V, all analog inputs

All analog outputs

0.7V<VRO<4.1V, VROi

VRO

VXI to GXO,RL on GXO>10kΩ

0.7V<VGX<4.1V, GXOi

GXO

RL=5000Ω

-200

200 nA

10

-10%

10

2.375

+10%

MΩ

pF

V

-10% 2.375 +10% V

5

2000

5000

5000

1

10000

2

1.12

10 Ω

Ω

Ω

100 pF

V/V

MHz

Ω

50 pF

Vrms

11 www.national.com

11 Page | ||

| Páginas | Total 19 Páginas | |

| PDF Descargar | [ Datasheet TP3094V.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| TP3094 | Quad PCM Codec/Filter | National Semiconductor |

| TP3094 | TP3094 COMBO Quad PCM Codec/Filter (Rev. B) | Texas Instruments |

| TP3094V | Quad PCM Codec/Filter | National Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |