|

|

PDF S-19190 Data sheet ( Hoja de datos )

| Número de pieza | S-19190 | |

| Descripción | VOLTAGE MONITORING IC | |

| Fabricantes | Seiko | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de S-19190 (archivo pdf) en la parte inferior de esta página. Total 24 Páginas | ||

|

No Preview Available !

S-19190 Series

www.sii-ic.com

FOR AUTOMOTIVE 105°C OPERATION

VOLTAGE MONITORING IC WITH CELL BALANCING FUNCTION

© SII Semiconductor Corporation, 2015-2016

Rev.1.3_00

The S-19190 Series is a voltage monitoring IC with a cell balancing function and includes a high-accuracy voltage

detection circuit and a delay circuit.

The S-19190 Series is suitable for cell balancing and overcharge protection of batteries and capacitors.

Caution This product can be used in vehicle equipment and in-vehicle equipment. Before using the product

in the purpose, contact to SII Semiconductor Corporation is indispensable.

Features

• High-accuracy voltage detection circuit

Cell balancing detection voltage: 2.0 V to 4.6 V (5 mV step)

Accuracy ±12 mV (2.0 V ≤ VBU < 2.4 V)

Cell balancing release voltage: 2.0 V to 4.6 V*1

Accuracy ±0.5% (2.4 V ≤ VBU ≤ 4.6 V)

Accuracy ±24 mV (2.0 V ≤ VBL < 2.4 V)

Accuracy ±1.0% (2.4 V ≤ VBL ≤ 4.6 V)

Overcharge detection voltage: 2.0 V to 4.6 V (5 mV step)

Accuracy ±12 mV (2.0 V ≤ VCU < 2.4 V)

Overcharge release voltage:

2.0 V to 4.6 V*2

Accuracy ±0.5% (2.4 V ≤ VCU ≤ 4.6 V)

Accuracy ±24 mV (2.0 V ≤ VCL < 2.4 V)

Accuracy ±1.0% (2.4 V ≤ VCL ≤ 4.6 V)

• Built-in Nch transistor with ON resistance of 5 Ω typ. between the CB pin and the VSS pin

• Current consumption:

2.0 μA max. (Ta = +25°C)

• Delay times are generated only by an internal circuit (External capacitors are unnecessary).

• CO pin output form and output logic are selectable: CMOS output

Active "H", active "L"

_____ Nch open-drain output Active "H", active "L"

• Switchable to power-saving mode by using the CE pin

• Operation temperature range:

Ta = −40°C to +105°C

• Lead-free (Sn 100%), halogen-free

• AEC-Q100 qualified*3

*1. Cell balancing release voltage = Cell balancing detection voltage − Cell balancing hysteresis voltage

(Cell balancing hysteresis voltage can be selected as 0 V or from a range of 0.1 V to 0.7 V in 50 mV step.)

*2. Overcharge release voltage = Overcharge detection voltage − Overcharge hysteresis voltage

(Overcharge hysteresis voltage can be selected as 0 V or from a range of 0.1 V to 0.7 V in 50 mV step.)

*3. Contact our sales office for details.

Applications

• Rechargeable battery module

• Capacitor module

Package

• SOT-23-6

1

1 page

FOR AUTOMOTIVE 105°C OPERATION VOLTAGE MONITORING IC WITH CELL BALANCING FUNCTION

Rev.1.3_00

S-19190 Series

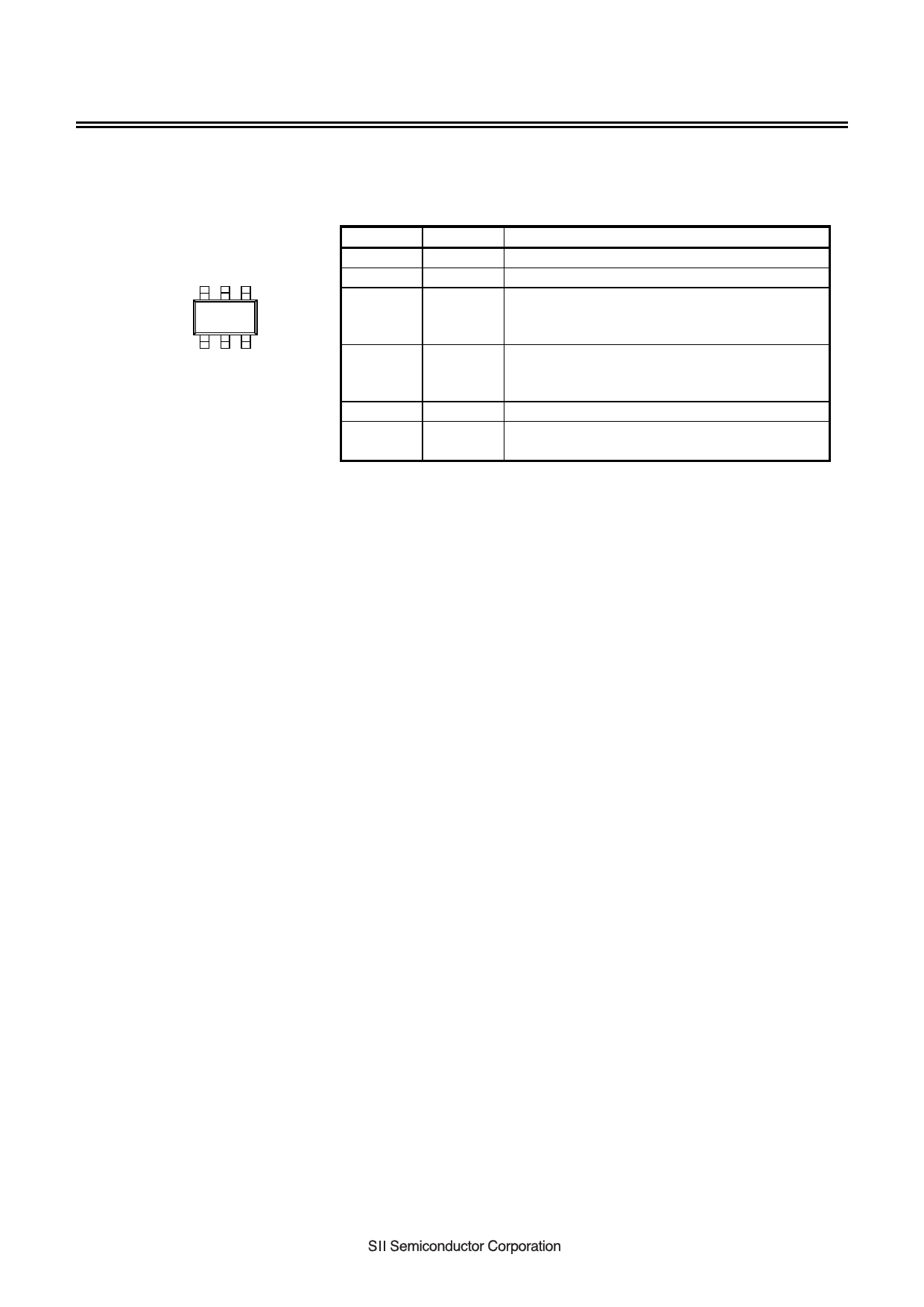

Pin Configuration

1. SOT-23-6

Top view

654

123

Figure 2

Pin No.

1

2

3

4

5

6

Symbol

CO

VSS

DP

_____

CE

VDD

CB

Table 5

Description

Output pin for overcharge signal

Input pin for negative power supply

Test mode switching pin

"H": Test mode (used to shorten the delay time)

"L": Normal operation mode

Power-saving mode switching pin

"H": Power-saving mode

"L": Normal operation mode

Input pin for positive power supply

Output pin for cell balancing signal

(Nch open-drain output)

5

5 Page

FOR AUTOMOTIVE 105°C OPERATION VOLTAGE MONITORING IC WITH CELL BALANCING FUNCTION

Rev.1.3_00

S-19190 Series

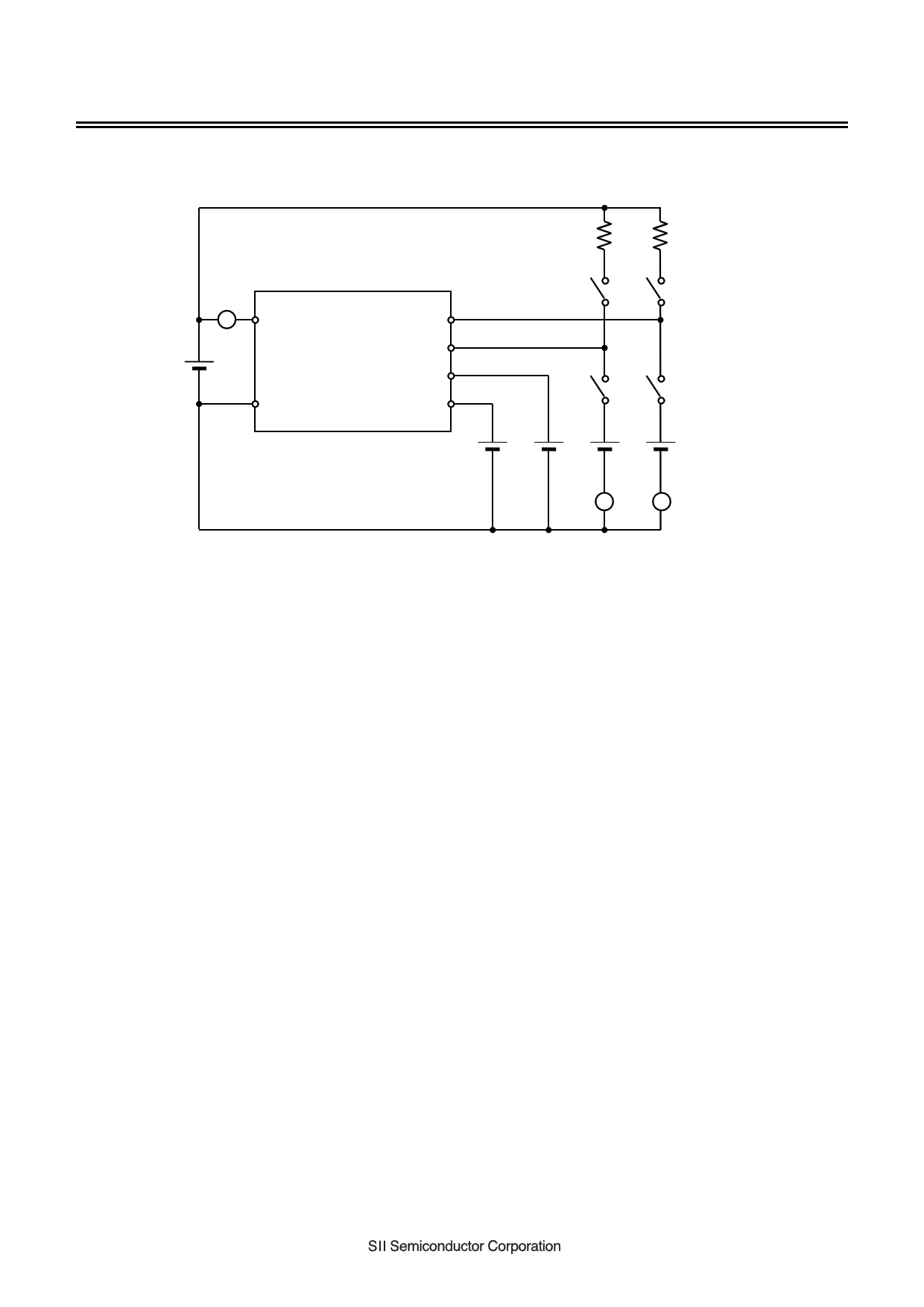

Test Circuit

RCB = 100 kΩ

RCO = 100 kΩ

IVDD

A

VDD

V1

VSS

S-19190

Series

CO

CB

DP

_____

CE

V2

SW1

SW2

V3 V4

SW3

SW4

V5

ICB A ICO A

Figure 3

Caution Unless otherwise specified in Table 8, set V2 = V3 = 0 V, and SWn (n = 1 to 4) = OFF.

_____

1. CE pin voltage "H"

_____

CE

pin

voltage

"H"

(V )_____

CEH

is

defined

as

the

voltage

at

which

IVDD

is

changed

from

IOPE

to

IPSV

when

V2

is

increased

from 0 V after setting V1 = VBL − 0.1 V.

_____

2. CE pin voltage "L"

_____

CE

pin

voltage

"L"

(V )_____

CEL

is

defined

as

the

voltage

at

which

IVDD

is

changed

from

IPSV

to

IOPE

when

V2

is

decreased

from VBL − 0.1 V after setting V1 = V2 = VBL − 0.1 V.

3. DP pin voltage "H"*1

DP pin voltage "H" (VDPH) is defined as the voltage at which the test mode is switched when V3 is increased from

0 V after setting V1 = VBL − 0.1 V.

4. DP pin voltage "L" *1

DP pin voltage "L" (VDPL) is defined as the voltage at which the normal operation mode is switched when V3 is

decreased from VBL − 0.1 V after setting V1 = V3 = VBL − 0.1 V.

5. Cell balancing detection delay time

Cell balancing detection delay time (tBU) is defined as the time from when SW1 is set to ON and V1 is set to VBU −

0.1 V to when the CB pin output is inverted after setting V1 to VBU + 0.1 V.

6. Cell balancing release delay time

Cell balancing release delay time (tBL) is defined as the time from when SW1 is set to ON and V1 is set to VBL +

0.1 V to when the CB pin output is inverted after setting V1 to VBL − 0.1 V.

7. Overcharge detection delay time

Overcharge detection delay time (tCU) is defined as the time from when SW1 is set to ON and V1 is set to VCU −

0.1 V to when the CO pin output is inverted after setting V1 to VCU + 0.1 V.

8. Overcharge release delay time

Overcharge release delay time (tCL) is defined as the time from when SW1 is set to ON and V1 is set to VCL +

0.1 V to when the CO pin output is inverted after setting V1 to VCL − 0.1 V.

*1. For details about switching to the test mode by using the DP pin, refer to "5. DP pin" in " Operation".

11

11 Page | ||

| Páginas | Total 24 Páginas | |

| PDF Descargar | [ Datasheet S-19190.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| S-19190 | VOLTAGE MONITORING IC | Seiko |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |