|

|

PDF MAX11100 Data sheet ( Hoja de datos )

| Número de pieza | MAX11100 | |

| Descripción | 200ksps ADC | |

| Fabricantes | Maxim Integrated | |

| Logotipo |  |

|

Hay una vista previa y un enlace de descarga de MAX11100 (archivo pdf) en la parte inferior de esta página. Total 21 Páginas | ||

|

No Preview Available !

MAX11100

16-Bit, +5V, 200ksps ADC with 10µA Shutdown

General Description

The MAX11100 low-power, 16-bit analog-to-digital con-

verter (ADC) features a successive-approximation ADC,

automatic power-down, fast 1.1Fs wake-up, and a high-

speed SPI/QSPI™/MICROWIRE®-compatible interface.

The MAX11100 operates with a single +5V analog supply

and features a separate digital supply, allowing direct

interfacing with 2.7V to 5.25V digital logic.

At the maximum sampling rate of 200ksps, the MAX11100

typically consumes 2.45mA. Power consumption is typi-

cally 12.25mW (VAVDD = VDVDD = +5V) at a 200ksps

(max) sampling rate. AutoShutdown™ reduces supply

current to 140FA at 10ksps and to less than 10FA at

reduced sampling rates.

Excellent dynamic performance and low power, com-

bined with ease of use and small package size (10-pin

FMAX® and 12-bump WLP), make the MAX11100 ideal

for battery-powered and data-acquisition applications

or for other circuits with demanding power consumption

and space requirements.

Applications

Motor Control

Industrial Process Control

Industrial I/O Modules

Data-Acquisition Systems

Thermocouple Measurements

Accelerometer Measurements

Portable- and Battery-Powered Equipment

Features

S 16-Bit Resolution, No Missing Codes

S +5V Single-Supply Operation

S Adjustable Logic Level (2.7V to 5.25V)

S Input Voltage Range: 0 to VREF

S Internal Track-and-Hold, 4MHz Input Bandwidth

S SPI/QSPI/MICROWIRE-Compatible Serial Interface

S Small 10-Pin µMAX and WLP Packages

S Low Power

2.45mA at 200ksps

140µA at 10ksps

0.1µA in Power-Down Mode

Functional Diagram

AVDD

DVDD

REF

AIN

AGND

SCLK

CS

TRACK-AND-

HOLD

16-BIT SAR

ADC

OUTPUT

BUFFER

CONTROL

MAX11100

DOUT

Ordering Information appears at end of data sheet.

DGND

QSPI is a trademark of Motorola, Inc.

MICROWIRE is a registered trademark of National Semiconductor Corp.

AutoShutdown is a trademark and µMAX is a registered trademark of Maxim Integrated Products, Inc.

For related parts and recommended products to use with this part, refer to: www.maximintegrated.com/MAX11100.related

For pricing, delivery, and ordering information, please contact Maxim Direct at

1-888-629-4642, or visit Maxim Integrated’s website at www.maximintegrated.com.

19-6046; Rev 1; 1/12

1 page

MAX11100

16-Bit, +5V, 200ksps ADC with 10µA Shutdown

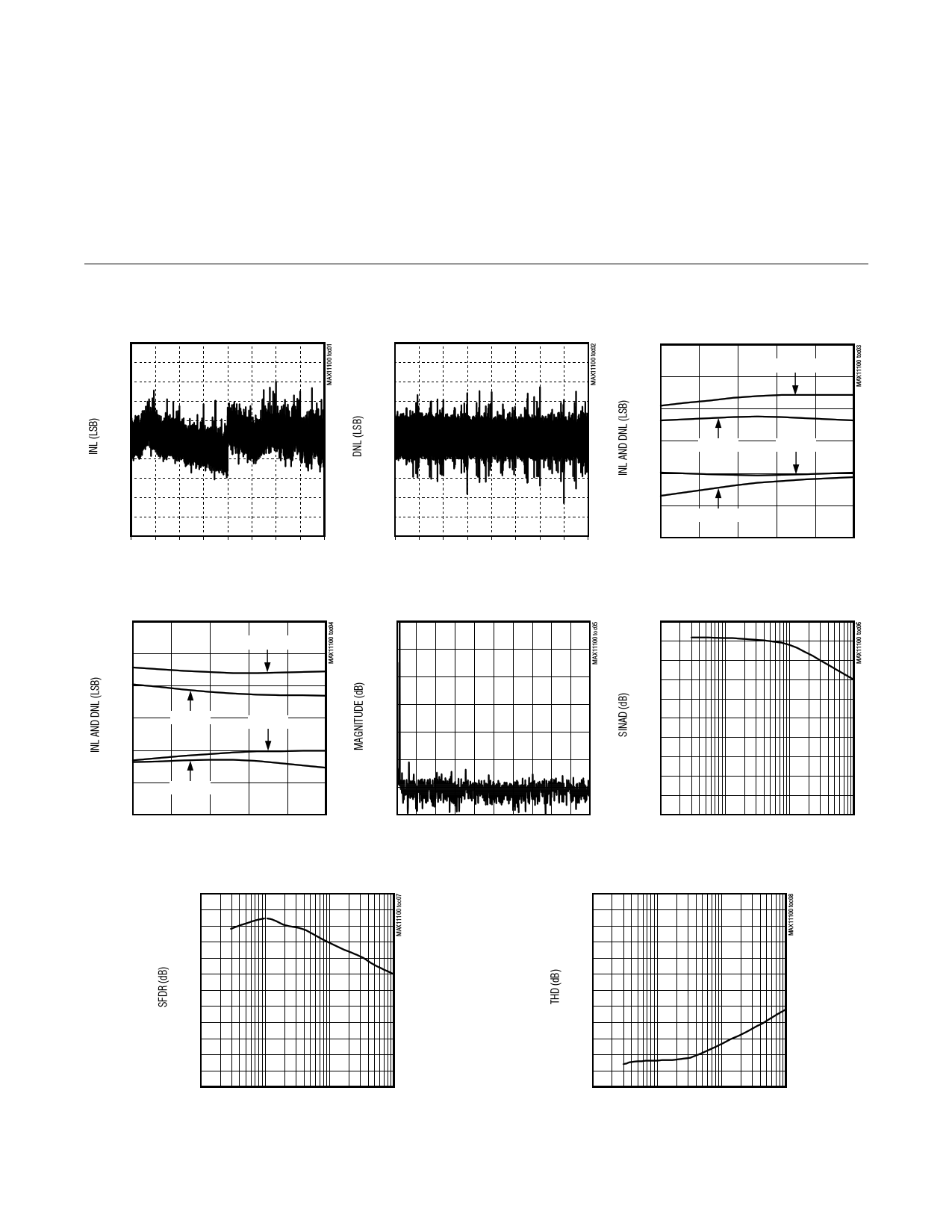

Typical Operating Characteristics

(VAVDD = VDVDD = 5V, fSCLK = 4.8MHz, CLOAD = 50pF, CREF = 4.7FF, VREF = 4.096V, TA = +25NC, unless otherwise noted.)

1.0

0.8

0.6

0.4

0.2

0

-0.2

-0.4

-0.6

-0.8

-1.0

0

INTEGRAL NONLINEARITY (INL)

vs. CODE

16384 32768 49152 65536

8192 24576 40960 57344

OUTPUT CODE (DECIMAL)

INL AND DNL vs. TEMPERATURE

1.5

MAX INL

1.0

0.5

0

MAX DNL

MIN DNL

-0.5

-1.0

-1.5

-40

MIN INL

-15 10 35 60

TEMPERATURE (°C)

85

120

110

100

90

80

70

60

50

40

30

20

10

0

0.1

SFDR vs. FREQUENCY

1 10

FREQUENCY (kHz)

DIFFERENTIAL NONLINEARITY (DNL)

vs. CODE

1.0

0.8

0.6

0.4

0.2

0

-0.2

-0.4

-0.6

-0.8

-1.0

0

16384 32768 49152 65536

8192 24576 40960 57344

OUTPUT CODE (DECIMAL)

INL AND DNL

vs. ANALOG SUPPLY VOLTAGE

1.5

MAX INL

1.0

0.5

0

MAX DNL

MIN DNL

-0.5

-1.0

MIN INL

-1.5

4.75 4.85 4.95 5.05 5.15 5.25

VAVDD (V)

MAX11100 FFT

0

-20

-40

-60

-80

-100

-120

-140

0 10 20 30 40 50 60 70 80 90 100

FREQUENCY (kHz)

0

-10

-20

-30

-40

-50

-60

-70

-80

-90

-100

-110

-120

100 0

SINAD vs. FREQUENCY

100

90

80

70

60

50

40

30

20

10

0

0 1 10

FREQUENCY (kHz)

TOTAL HARMONIC DISTORTION

vs. FREQUENCY

1 10

FREQUENCY (kHz)

100

100

Maxim Integrated

5

5 Page

MAX11100

16-Bit, +5V, 200ksps ADC with 10µA Shutdown

CS

SCLK

DOUT

tDV

1

tCSS

4 6 8 12 16 20 24

tCL

tCH

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0 tCSH

tACQ tDO

tTR

Figure 6. External Timing Diagram

COMPLETE CONVERSION SEQUENCE

CS

DOUT

TIMING NOT TO SCALE.

CONVERSION 0

POWERED UP

POWERED DOWN

CONVERSION 1

POWERED UP

Figure 7. Shutdown Sequence

Variations in frequency, duty cycle, or other aspects of

the clock signal’s shape result in changing offset.

A CS falling edge initiates an acquisition sequence. The

analog input is stored in the capacitive DAC, DOUT

changes from high impedance to logic-low, and the ADC

begins to convert after the sixth clock cycle. SCLK drives

the conversion process and shifts out the conversion

result on DOUT.

SCLK begins shifting out the data (MSB first) after the fall-

ing edge of the 8th SCLK pulse. Twenty-four falling clock

edges are needed to shift out the eight leading zeros

and 16 data bits. Extra clock pulses occurring after the

conversion result has been clocked out, and prior to the

rising edge of CS, produce trailing zeros at DOUT and

have no effect on the converter operation.

Force CS high after reading the conversion’s LSB to

reset the internal registers and place the MAX11100 in

shutdown. For maximum throughput, force CS low again

to initiate the next conversion immediately after the speci-

fied minimum time (tCSW).

Note: Forcing CS high in the middle of a conversion

immediately aborts the conversion and places the

MAX11100 in shutdown.

Maxim Integrated

11

11 Page | ||

| Páginas | Total 21 Páginas | |

| PDF Descargar | [ Datasheet MAX11100.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| MAX1110 | Serial 8-Bit ADCs | Maxim Integrated |

| MAX11100 | 200ksps ADC | Maxim Integrated |

| MAX11101 | 200ksps ADC | Maxim Integrated |

| MAX11102 | Serial 12-/10-/8-Bit ADCs | Maxim Integrated Products |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |