|

|

PDF NB3H83905C Data sheet ( Hoja de datos )

| Número de pieza | NB3H83905C | |

| Descripción | 1.8V/2.5V/3.3V Crystal Input to 1:6 LVTTL/LVCMOS Clock Fanout Buffer | |

| Fabricantes | ON Semiconductor | |

| Logotipo | ||

Hay una vista previa y un enlace de descarga de NB3H83905C (archivo pdf) en la parte inferior de esta página. Total 15 Páginas | ||

|

No Preview Available !

NB3H83905C

1.8V/2.5V/3.3V Crystal Input

to 1:6 LVTTL/LVCMOS Clock

Fanout Buffer with OE

Description

The NB3H83905C is a 1.8 V, 2.5 V or 3.3 V VDD core Crystal input

to 1:6 LVTTL/LVCMOS fanout buffer with outputs powered by

flexible 1.8 V, 2.5 V, or 3.3 V supply VDDO (with VDD w VDDO). The

device accepts a fundamental Parallel Resonant crystal from 3 MHz to

40 MHz or a single−ended LVCMOS Clock from up to 100 MHz.

Two synchronous LVTTL/LVCMOS Enable lines permit

independent control over outputs BCLK[0:4] and output BCLK5;

enabling or disabling only when the output is in LOW state

eliminating potential output glitching or runt pulse generation. When

unused, leave floating open, pins will default to HIGH state.

The 6 outputs drive 50 W series or parallel terminated transmission

lines. Parallel termination should be to 1/2 VCC. Series terminated

lines can drive 2 loads each, or 12 lines total.

Fit, Form, and Function compatible with ICS83905 and PI6C10806.

Features

• Six Copies of LVTTL/LVCMOS Output Clock

• Supply Operation VDD w VDDO:

♦ 1.8 V$0.2 V, 2.5 V $5% or 3.3 V $5% Core VDD

♦ 1.8 V$0.2 V, 2.5 V $5%, or 3.3 V $5% Output VDDO

• Crystal Oscillator Interface

• Crystal Input Frequency Range: 3 MHz to 40 MHz

• Clock Input Frequency Range: Up to 100 MHz

• LVCMOS compatible Enable Inputs

• 5 V Tolerant Enable Inputs

• Low Output to Output Skew: 80 ps Max

• Synchronous Output Enable

• Phase Noise Floor −160 dBc (1 MHz)

• Industrial Temperature Range

• These are Pb−Free Devices

XTAL_IN/CLK

XTAL_OUT

C1

C2

ENABLE1

ENABLE2

SYNC

SYNC

BCLK0

BCLK1

BCLK2

BCLK3

BCLK4

BCLK5

Figure 1. Simplified Block Diagram

http://onsemi.com

MARKING

DIAGRAMS*

16

SOIC−16

D SUFFIX

CASE 751B

NB3H83905G

ALYYWW

1

16

1

TSSOP−16

DT SUFFIX

CASE 948F

16

NB3H

905C

ALYWG

G

1

1

QFN20

MN SUFFIX

CASE 485BH

20

1 NB3H

83905

ALYWG

G

A = Assembly Location

L = Wafer Lot

YY, Y = Year

WW, W = Work Week

G or G = Pb−Free Package

(*Note: Microdot may be in either location)

*For additional marking information, refer to

Application Note AND8002/D.

ORDERING INFORMATION

See detailed ordering and shipping information in the package

dimensions section on page 11 of this data sheet.

© Semiconductor Components Industries, LLC, 2012

November, 2012 − Rev. 9

1

Publication Order Number:

NB3H83905C/D

1 page

NB3H83905C

Table 6. DC CHARACTERISTICS

Symbol

Characteristic

Min Typ Max Unit

VDD = VDDO = 3.135 V to 3.465 V (3.3 V $5%); GND = 0 V, TA = −405C to +855C

IDD Core Quiescent Power Supply Current (ENABLEx = LOW)

10 mA

IDDO Output Quiescent Power Supply Current (ENABLEx = LOW)

5 mA

VIH Input HIGH Voltage ENABLEx, XTAL_IN/CLK

2

VDD +

V

0.3 V

VIL Input LOW Voltage ENABLEx, XTAL_IN/CLK

VOH Output HIGH Voltage (Note 4)

VOL Output LOW Voltage (Note 4)

CIN Input Capacitance

CPD Power Dissipation Capacitance (per Output) (Note 4)

ROUT Output Impedance (Note 4)

VDD = VDDO = 2.375 V to 2.625 V (2.5 V $5%); GND = 0 V, TA = −405C to +855C

IDD Core Quiescent Power Supply Current (ENABLEx = LOW)

−0.3

2.6

4

19

7

0.8 V

V

0.5 V

pF

pF

W

8 mA

IDDO Output Quiescent Power Supply Current (ENABLEx = LOW)

4 mA

VIH Input HIGH Voltage ENABLEx, XTAL_IN/CLK

1.7

V0D.3DV+

V

VIL Input LOW Voltage ENABLEx, XTAL_IN/CLK

VOH

Output

Output

HIGH

HIGH

Voltage

Voltage

((NIOoHte=4−)1

mA)

−0.3 0.7 V

2.0 V

1.8

VOL Output LOW Voltage (IOL = 1 mA)

Output LOW Voltage (Note 4)

0.4 V

0.45

CIN Input Capacitance

CPD Power Dissipation Capacitance (per Output) (Note 4)

ROUT Output Impedance (Note 4)

VDD = VDDO = 1.6 V to 2.0 V (1.8 V $0.2 V); GND = 0 V, TA = −405C to +855C

IDD Core Quiescent Power Supply Current (ENABLEx = LOW)

4 pF

18 pF

7W

5 mA

IDDO Output Quiescent Power Supply Current (ENABLEx = LOW)

3 mA

VIH Input HIGH Voltage ENABLEx, XTAL_IN/CLK

0.65*VDD

V0D.3DV+

V

VIL Input LOW Voltage ENABLEx, XTAL_IN/CLK

−0.3

0.35*VDD

V

VOH Output HIGH Voltage (Note 4)

VDDO−0.3

V

VOL Output LOW Voltage (Note 4)

0.35 V

CIN Input Capacitance

4 pF

CPD Power Dissipation Capacitance (per Output) (Note 4)

16 pF

ROUT Output Impedance (Note 4)

10 W

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit

board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared

operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification

limit values are applied individually under normal operating conditions and not valid simultaneously.

4. Parallel terminated 50 W to VDDO/2 (see Figure 5).

http://onsemi.com

5

5 Page

NB3H83905C

APPLICATION INFORMATION

Crystal Input Interface

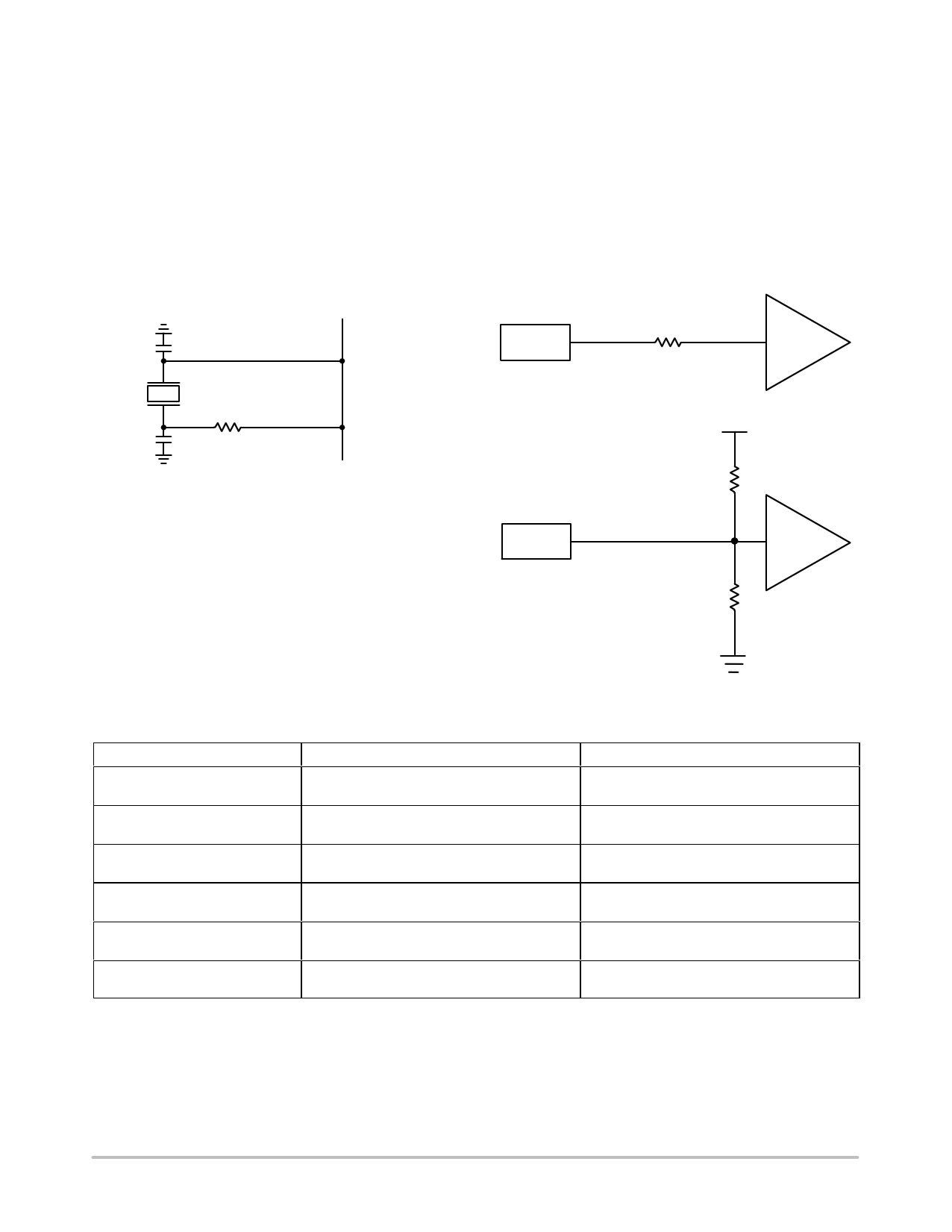

Figure 8 shows the NB3H83905C device crystal

oscillator interface using a typical parallel resonant crystal.

A parallel crystal with loading capacitance CL = 18 pF

would use C1 = 32 pF and C2 = 32 pF as nominal values,

assuming 4 pF of stray cap per line. The frequency accuracy

and duty cycle skew can be fine tuned by adjusting the C1

and C2 values. For example, increasing the C1 and C2

values will reduce the operational frequency. Note R1 is

optional and may be 0 W.

Unused Input and Output Pins

All LVCMOS control pins have internal pull−ups or

pull−downs; additional external resistors are not required

(optionally 1 kW resistors may be used). All unused

LVCMOS outputs can be left floating with no trace attached.

Bypass

The VDD and VDDO supply pins should be bypassed with

both a 10 mF and a 0.1 mF cap from supply pins to GND.

32 pF

32 pF

C1 XTAL_IN/CLK

X1 18 pF

Parallel Resonant

Crystal

C2 R1*

XTAL_OUT

NB3H83905C

BCLKx

Rseries = 28 W

LVCMOS

Figure 9. Series Termination

Figure 8. NB3H83905C Crystal Oscillator Interface

* R1 is optional

R = 100 W

Termination

NB3H83905C device output series termination may be

used by locating a 28 W series resistor at the driver pin as

shown in Figure 9. Alternatively, a Thevenin Parallel

termination may be used by locating a 100 W pullup resistor

to VDD and a 100 W pullup resistor to GND at the receiver

pin, instead of an Rs source termination resistor, Figure 10.

BCLKx

R = 100 W

LVCMOS

Figure 10. Optional Thevenin Termination

ORDERING INFORMATION

Device

Package

Shipping†

NB3H83905CDG

SOIC−16

(Pb*Free)

48 Units / Rail

NB3H83905CDR2G

SOIC−16

(Pb*Free)

2500 Units / Tape & Reel

NB3H83905CDTG

TSSOP−16

(Pb*Free)

96 Units /Rail

NB3H83905CDTR2G

TSSOP−16

(Pb*Free)

2500 Units / Tape & Reel

NB3H83905CMNG

QFN−20

(Pb−Free)

92 Units / Rail

NB3H83905CMNTXG

QFN−20

Pb−Free)

3000 / Tape & Reel

†For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging

Specifications Brochure, BRD8011/D.

http://onsemi.com

11

11 Page | ||

| Páginas | Total 15 Páginas | |

| PDF Descargar | [ Datasheet NB3H83905C.PDF ] | |

Hoja de datos destacado

| Número de pieza | Descripción | Fabricantes |

| NB3H83905C | 1.8V/2.5V/3.3V Crystal Input to 1:6 LVTTL/LVCMOS Clock Fanout Buffer | ON Semiconductor |

| Número de pieza | Descripción | Fabricantes |

| SLA6805M | High Voltage 3 phase Motor Driver IC. |

Sanken |

| SDC1742 | 12- and 14-Bit Hybrid Synchro / Resolver-to-Digital Converters. |

Analog Devices |

|

DataSheet.es es una pagina web que funciona como un repositorio de manuales o hoja de datos de muchos de los productos más populares, |

| DataSheet.es | 2020 | Privacy Policy | Contacto | Buscar |